CY7C67200

Document #: 38-08014 Rev. *G

Page 62 of 78

Receive Full

(Bit 1)

The Receive Full bit indicates whether the receive buffer is full.

It can be programmed to interrupt the CPU as interrupt #5

when the buffer is full. This can be done though the UART bit

of the Interrupt Enable register (0xC00E). This bit will automat-

ically be cleared when data is read from the UART Data

register.

1:

Receive buffer full

0:

Receive buffer empty

Transmit Full

(Bit 0)

The Transmit Full bit indicates whether the transmit buffer is

full. It can be programmed to interrupt the CPU as interrupt #4

when the buffer is empty. This can be done though the UART

bit of the Interrupt Enable register (0xC00E). This bit will

automatically be set to ‘1’ after data is written by EZ-Host to

the UART Data register (to be transmitted). This bit will

automatically be cleared to ‘0’ after the data is transmitted.

1:

Transmit buffer full (transmit busy)

0:

Transmit buffer is empty and ready for a new byte of data

UART Data Register [0xC0E4] [R/W]

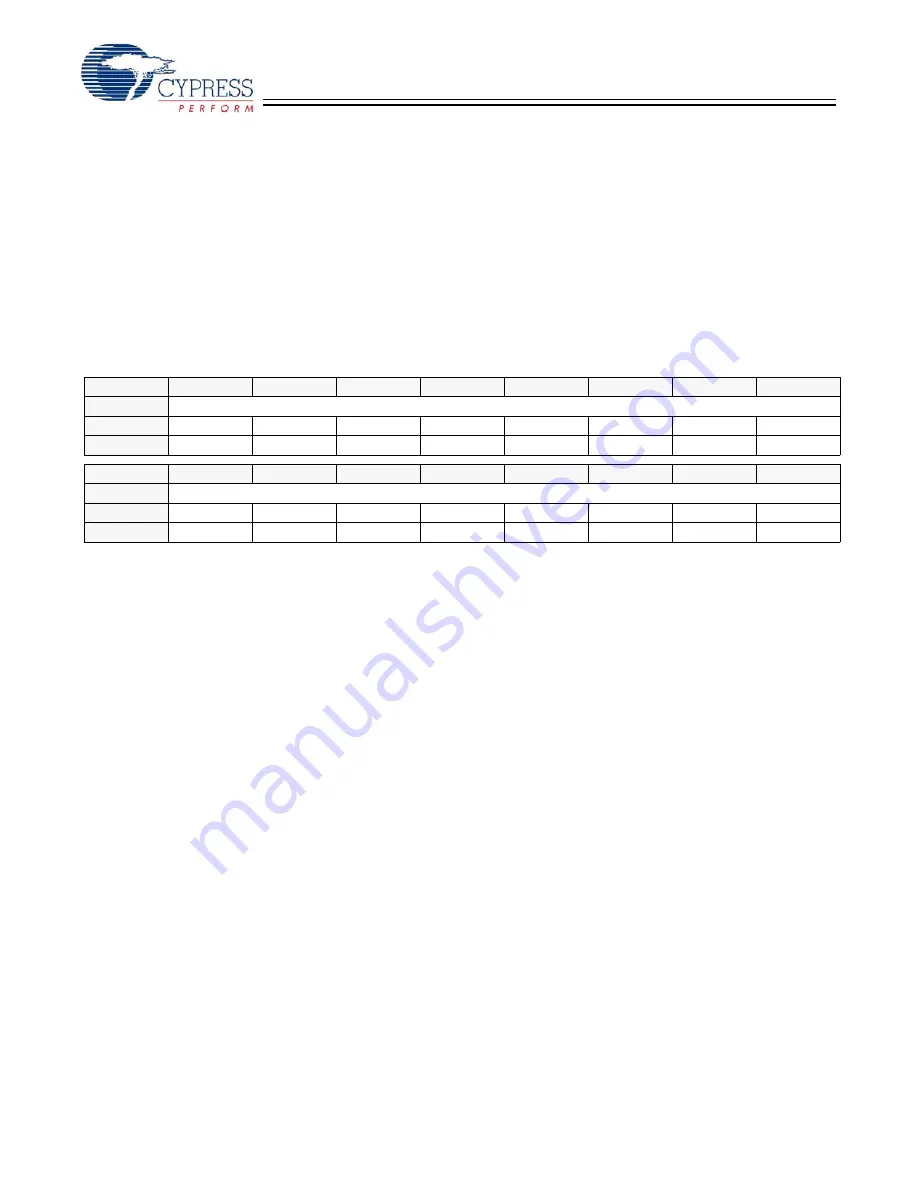

Figure 75. UART Data Register

Register Description

The UART Data register contains data to be transmitted or received from the UART port. Data written to this register will start a

data transmission and also causes the UART Transmit Empty Flag of the UART Status register to set. When data received on

the UART port is read from this register, the UART Receive Full Flag of the UART Status register will be cleared.

Data

(Bits [7:0])

The Data field is where the UART data to be transmitted or received is located

Reserved

All reserved bits must be written as ‘0’.

Bit #

15

14

13

12

11

10

9

8

Field

Reserved

Read/Write

-

-

-

-

-

-

-

-

Default

0

0

0

0

0

0

0

0

Bit #

7

6

5

4

3

2

1

0

Field

Data

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

[+] Feedback