-50-

IC DESCRIPTION

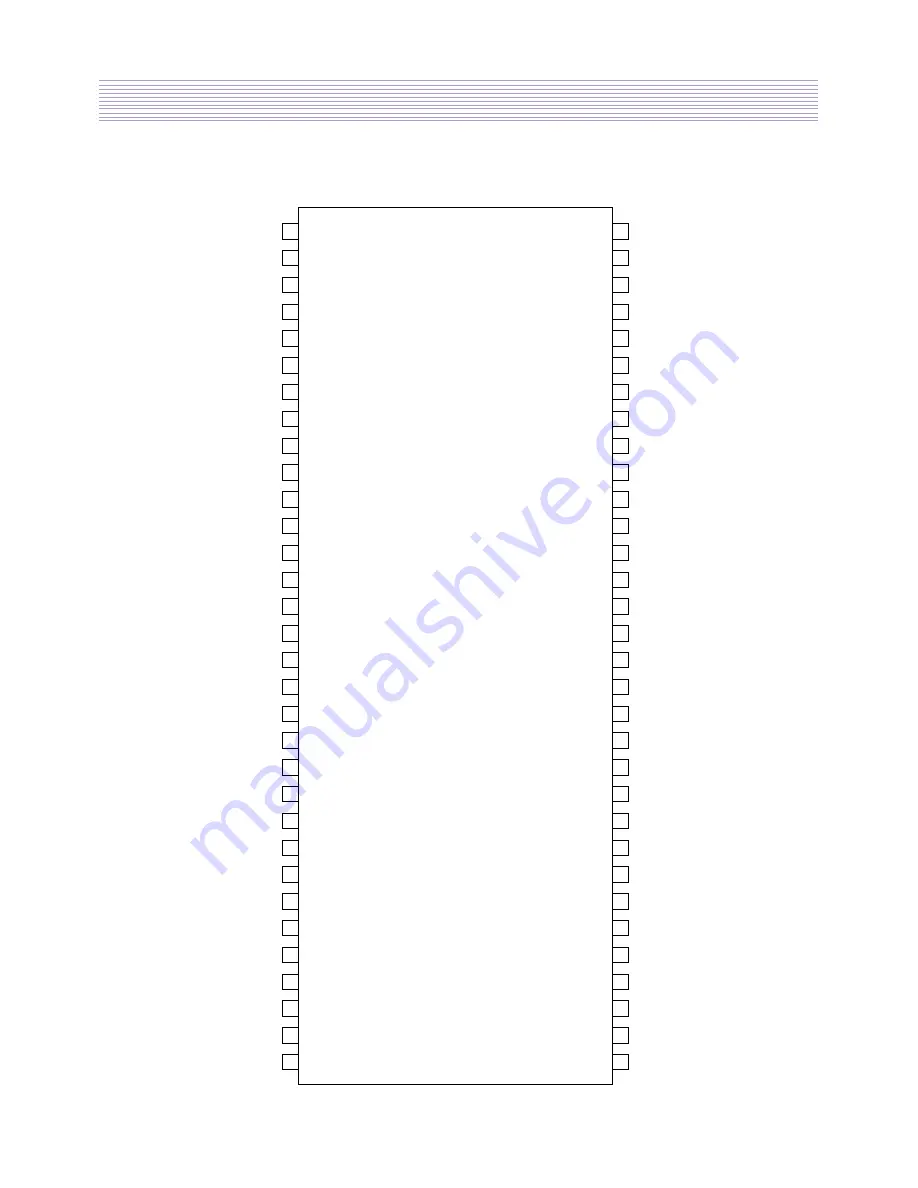

3. Pin Congration

TEST

RESQ

SCL

SDA

GNDD

HCS

FSY

CSU

VS

INTLC

VPROT

SAFETU

HFLB

GNDD

VSUPD

GNDD

VSUPD

P0

P1

P2

P3

P4

P5

P6

GNDD

RSW2

RSW1

SENSE

GNDM

VERTQ

VERT

E/W

VIN4

VIN3

VIN2

VIN1

CIN1

VOUT

VSUPAF

VRT

SGND

GNDAF

CBIN

CIN2/CRIN

XTAL2

XTAL1

HOUT

CLK20

FBLIN2

BIN2

GIN2

RIN2

FBLIN

BIN

GIN

RIN

VRD

BOUT

GOUT

ROUT

VSUPAB

GNDAB

SVMOUT

XREF

I501

VDP3130Y

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

Appendix

Summary of Contents for DTQ-20U4SC

Page 7: ...6 CIRCUIT BLOCK DIAGRAM...

Page 14: ...13 SCHEMATIC DIAGRAM 20U4 SHEET 1...

Page 15: ...14 SCHEMATIC DIAGRAM 20U4 SHEET 2...

Page 16: ...15 SCHEMATIC DIAGRAM 27U4 SHEET 1...

Page 17: ...16 SCHEMATIC DIAGRAM 27U4 SHEET 2...

Page 46: ...45 PRINTED CIRCUIT BOARD CN 230F MAIN...

Page 47: ...46 PRINTED CIRCUIT BOARD CN 230F 20U4 CRT...

Page 48: ...47 PRINTED CIRCUIT BOARD CN 230F 27U4 CRT...

Page 57: ...56 WAVEFORMS Appendix 17 SVM Q909 BASE 18 I901 PIN7 ROUT...

Page 64: ...PRINTED DATE Mar 2003...