-34-

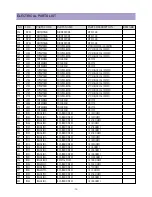

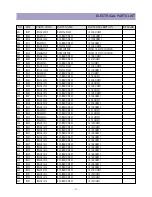

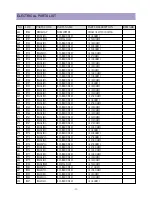

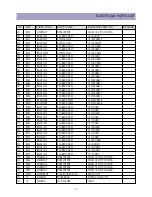

IC DESCRIPTION

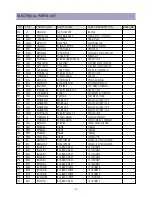

Appendix

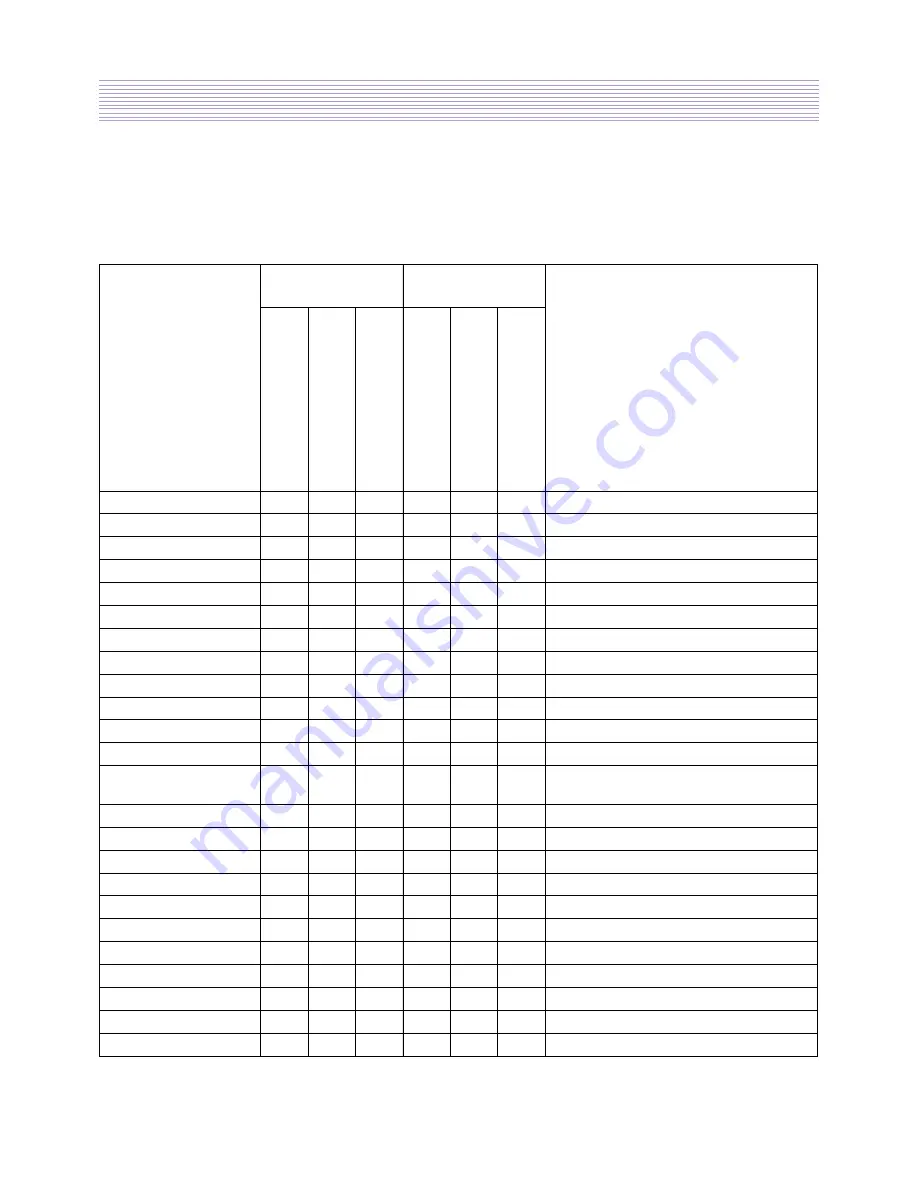

2. Pin Description

SYMBOL

STANDARD

VERSION

FACE DOWN

VERSION

DESCRIPTION

A

V

STEREO QFP128

FULL-STEREO/

MONO+ A

V

STEREO SSDIP90

MONO

A

V

STEREO QFP128

FULL-STEREO/

MONO+ A

V

STEREO SSDIP90

MONO

VSSP2

1

1

128

90

ground

VSSC4

2

1

127

90

ground

VDDC4

3

3

126

88

digital supply to SDACs (1.8V)

VDDA3(3.3V)

4

16

125

75

supply (3.3 V)

VREF_POS_LSL

5

16

124

75

positive reference voltage SDAC (3.3 V)

VREF_HPL

6

17

123

74

negative reference voltage SDAC (0 V)

VREF_HPR

7

16

122

75

positive reference voltage SDAC (3.3 V)

VREF_HPR

8

17

121

74

negative reference voltage SDAC (0 V)

VREF_POS_HPR

9

16

120

75

positive reference voltage SDAC (3.3 V)

XTALIN

10

18

119

73

crystal oscillator input

XTALOUT

11

19

118

72

crystal oscillator output

VSSA1

12

20

117

71

ground

VGUARD/SWIO

13

69

116

22

V-guard input / I/O switch (e.g. 4 mA current

sinking capability for direct drive of LEDs)

DECDIG

14

21

115

70

decoupling digital supply

VP1

15

22

114

69

1

st

supply voltage TV-processor (+5 V)

PH2LF

16

23

113

68

phase-2 lter

PH1LF

17

24

112

67

phase-1 lter

GND1

18

25

111

66

ground 1 for TV-processor

SECPLL

19

26

110

65

SECAM PLL decoupling

DECBG

20

27

109

64

bandgap decoupling

EWD/AVL

(1)

21

66

108

25

East-West drive output or AVL capacitor

VDRB

22

68

107

23

vertical drive B output

VDRA

23

67

106

24

vertical drive A output

VIFIN1

24

28

105

63

IF input 1

Summary of Contents for DTQ-29U1SCV

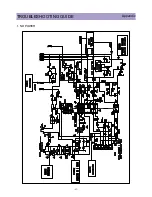

Page 7: ...6 CIRCUIT BLOCK DIAGRAM...

Page 27: ...26...

Page 28: ...27...

Page 31: ...30...

Page 32: ...31...

Page 33: ...32...