Document: After-sales Maintenance Service Manual No.: L32R63*VKE/L40R63*VKE/L43R63*VKE/L49R63*VKE Version: 1.0 Effective from: APRIL 4th, 2016

Page 30 of 49

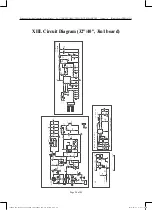

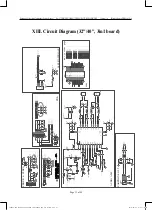

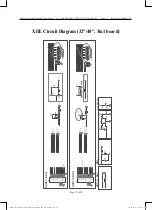

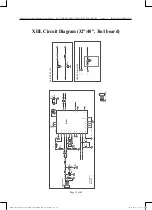

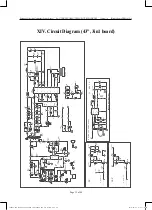

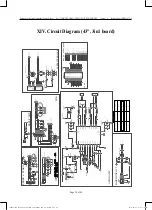

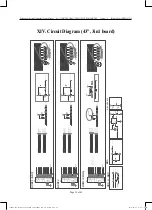

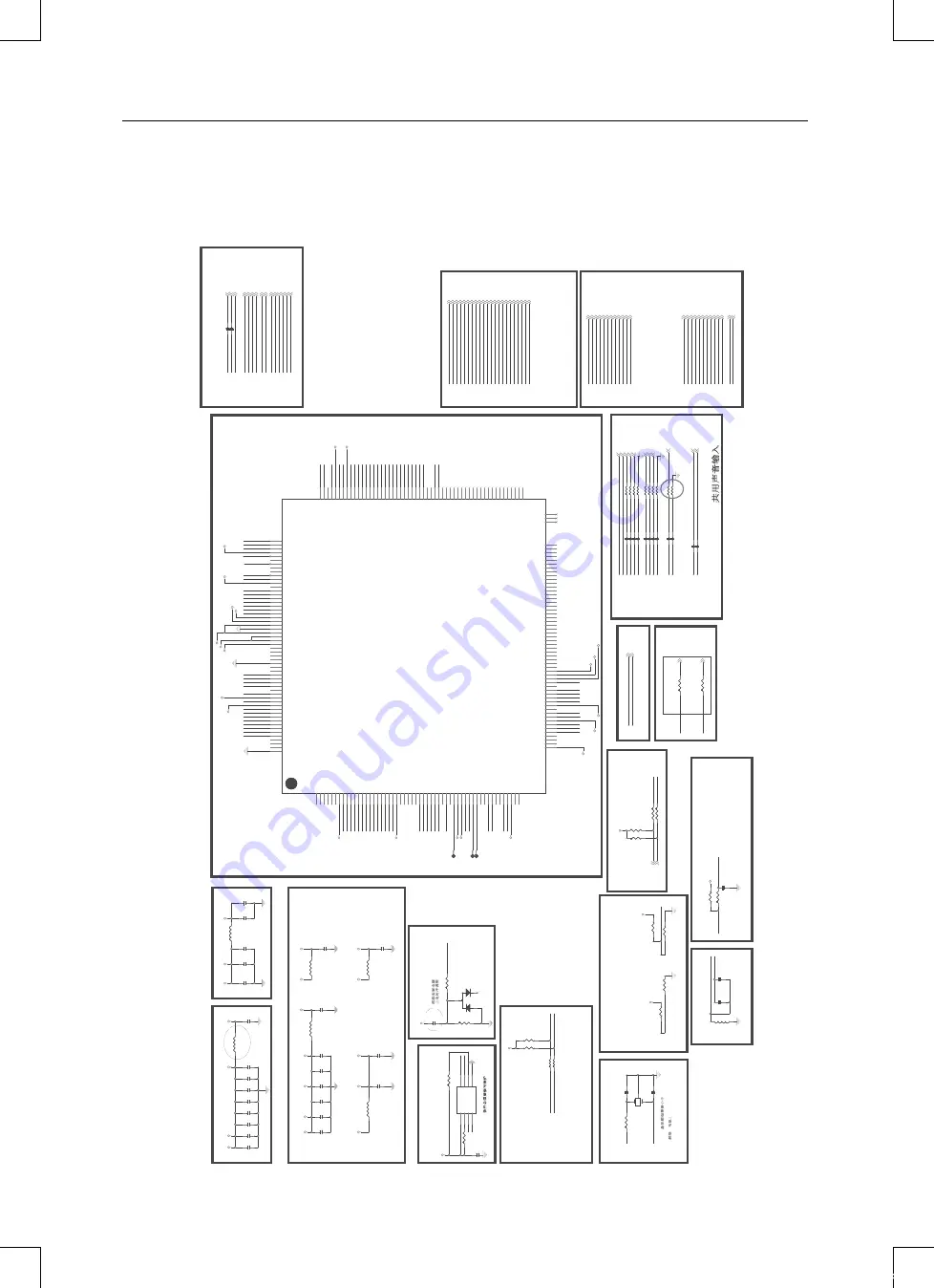

XIII. Circuit Diagram (32"/40", 3in1 board)

HDMI_CEC

HDMI2_CLKN

HDMI2_HPDIN

HDMI2_RX0N

HDMI2_RX2P

HDMI2_RX1N

HDMI2_RX2N

HDMI2_RX1P

HDMI2_SDA

HDMI2_SCL

HDMI2_CLKP

HDMI2_RX0P

HDM

I2_

SDA

HDM

I2_

SCL

SPI_

DO

UART_

RX

UART_

TX

KEY_SAR

1

MH

L_C

ABLE

-DE

T

KEY_SAR

0

RXE2-

RXO1+

RXE1+

RXEC+ RXE3-

RXE4+

RXO4+

RXO0-

RXE0-

RXO4-

RXO3+

RXO0+

RXE0+

RXE2+

RXO1-

RXE1-

RXEC-

RXE3+

RXO2-

RXE4-

RXO2+ RXO3-

HDM

I0_

RX2

P

HDM

I0_

RX2

N

HDM

I0_

RX0

N

HDM

I0_

RX0

P

HDM

I0_C

LK

N

HDM

I0_

RX1

N

HDM

I0_

RX1

P

HDM

I2_

HPDIN

AVDD5V

_M

HL

ARC

HDM

I0_C

LK

P

HDM

I_CEC

HDM

I0_

HPDIN

AMP-MUTE

HDMI0_SCL HDMI0_SDA HDMI0_HPDIN

HDMI0_RX2P

HDMI0_RX1N

HDMI0_RX2N

HDMI0_RX1P

HDMI0_CLKN HDMI0_CLKP

HDMI0_RX0P

HDMI0_RX0N

VGA_VS

BIN0

RIN2

RIN0

GIN0M

GIN0P

VGA_HS

VCOM0

GIN2P GIN2M

BIN2

CVBS0

HDMI2_CLKN

HDMI2_RX2P

HDMI2_RX1N

HDMI2_RX2N

HDMI2_RX1P

HDMI2_CLKP

HDMI2_RX0P

HDMI2_RX0N

PANEL_ON/OFF

IFAGC_T

PWR_ON/OFF

PANEL_ON/OFF

TUNER_SCL TUNER_SDA

BRI_ADJ-PWM0

HDM

I0_

SDA

HDM

I0_

SCL

VIF

M

VIF

P

IFA

GC-

T

XTALI

XTALO

MHL_CABLE-DET

ARC

SPI_WP

SPI_DO

SPI_DI

SPI_CSN

SPI_CLK

XTALO

System-RST

PWM1

BRI_ADJ-PWM0

IFAGC-T

IFAGC_T

VBL_CTRL

VCOM0

CVBS0

RIN2

BIN0

GIN0M

GIN0P

RIN0

VGA_HS VGA_VS

GIN2P GIN2M

BIN2

AV-IN

AUR4 AUL4

AUVRM

AUVAG

VIFM

VIFP

USB1_DP USB1_DM

AUVRM AUVAG

AUR4

AUL4

HDMI0_DEC

TUNER_SDA

TUNER_SCL

M-SCL M-SDA

UART_TX UART_RX

M-S

DA

M-S

CL

PWR

_O

N/O

FF

HDM

I0_

DEC

VBL_

CTRL

AMP-MUTE

RXE3+

RXE3-

RXEC-

USB1_DP USB1_DM

RXEC+

RXO4- RXO4+

RXO0+

RXE1-

RXO0-

RXO1- RXO1+

RXE2-

RXE0+

RXE0-

RXE1+

RXO2-

RXE2+

RXO2+ RXO3- RXO3+

RXE4- RXE4+

IRIN

PWM

1

Syste

m-R

ST

BRI_

ADJ-

PWM

0

AMP-AUOUTL AMP-AUOUTR

AMP-AUOUTR

AMP-AUOUTL

XTALI

IRIN KEY_SAR0 KEY_SAR1

LED

LED

SPI_

CLK

SPI_

DI

SPI_

CSN

AVDD_EAR33

VDDC

VDDC

AVDD_MOD1

DVDD_DDR

AVDDL_DVI

AVDD_MOD

AVDD3P3_ADC

AVDD_DDR_DATA

AVDD_DDR_CMD

AVDD_DMPLL

VDDC

AVDD_DADC

AVDD_ETH

+1.15V_VDDC

AVDDL_DVI

DVDD_DDR

VDDC

+1.5V_DDR

AVDD_DDR_CMD

AVDD_DDR_DATA

AVDD_MOD1

+3.3V_Standby

AVDD_MOD

AVDD_AU33

AVDD_EAR33

AVDD_DADC

+3.3V_Standby

AVDD3P3_ADC

AVDD_DMPLL

+3.3V_Standby

+3.3V_Standby

+5V_Standby

+3.3V_Standby

+3.3V_Standby

+3.3V_TU

AVDD5V_MHL

AVDD_ETH

+3.3V_Standby

AVDD_AU33

+5V_Standby

AVDD_MOD

AVDD_DDR_CMD

VDDC

VDDC

AVDD_MOD

VDDC

+3.3V_TU

HDMI2_SC

L

7

HDMI2_HPDI

N

7

HDMI2_CLK

N

7

HDMI2_SD

A

7

HDMI_CE

C

7

HDMI2_RX0

P

7

HDMI2_RX1

N

7

HDMI2_RX1

P

7

HDMI2_RX0

N

7

HDMI0_AR

C

7

PWR_ON/OF

F

3

RXE0

+

6

RXE0

-

6

RXE2

-

6

RXE1

+

6

RXE1

-

6

RXEC

+

6

RXEC

-

6

RXE2

+

6

RXE4

-

6

RXE3

+

6

RXE3

-

6

RXE4

+

6

RXO0

+

6

RXO0

-

6

RXO2

-

6

RXO1

+

6

RXO1

-

6

RXO3

-

6

RXO2

+

6

RXO4

+

6

RXO4

-

6

RXO3

+

6

AMP_MUT

E

6

MHL_CABLE_DE

T

7

HDMI0_RX0

N

7

HDMI0_RX0

P

7

HDMI0_RX2

P

7

HDMI0_RX1

N

7

HDMI0_RX1

P

7

HDMI0_CLK

N

7

HDMI0_CLK

P

7

HDMI0_RX2

N

7

HDMI0_SD

A

7

HDMI0_SC

L

7

HDMI0_HPDI

N

7

DIF

-

8

DIF

+

8

BRI_AD

J

4

PANEL_ON/OF

F

4

TUNER_SC

L

8

IFAGC_

T

8

HDMI2_CLK

P

7

HDMI2_RX2

N

7

HDMI2_RX2

P

7

AMP-IN

R

6

VBL_CTR

L

4

AV-I

N

6

YPbPr-P

B

6

YPbPr-P

R

6

YPbPr-

Y

6

VGA-HSYN

C

6

VGA-VSYN

C

6

VGA-

B

6

VGA-

G

6

VGA-

R

6

AV-LI

N

6

AV-RI

N

6

TUNER_SD

A

8

USB1_D

P

6

USB1_D

M

6

AMP-IN

L

6

HDMI0_DE

C

7

UART-RX

6

UART-TX

6

LE

D

4

IRI

N

4

KEY_SAR

1

4

KEY_SAR

0

4

MHL Port

SAR1--> SC-HSYNC

CORE POWER

DDR3 POWER

Standby Power 3.3V

软

件

必

须

要

做

写

保

护

SPI NOR FLASH

NOTE:

晶

体

频

偏

需

要

小

于

30PPM

Crystal

C1

C2

删

除

1M

电

阻

!

根

据

实

际

电

源

上

电

时

序

调

整

RESET

IC Configuration Selection

Audio Line Out

Audio Line IN YPBPR/AV/VG

A

共

用

声

音

输

入

VGA

YPBPR

AV

AUDIO LINE IN

HDMI

LVDS

OTHER

CHIP_CONFIG[1:0] {PAD_PWM1, PAD_PWM0} 2'b01 Boot from SPI_NOR Flash 2'b10 Boot from ROM

Close to MSTAR IC with width trace

IF AGC

不能省掉!

close to IC

EEPROM

MUST pull high to 5VSTB

ISP AND VGA EDID

DEBUG

IC

C293

0.1uF

C293

0.1uF

R26

3

10K

R26

3

10K

R29

7

68R

R29

7

68R

C21

2

47nF

C21

2

47nF

D202

BAV99

D202

BAV99

3

1

2

R25

4

10K

R25

4

10K

C232

0.1uF

C232

0.1uF

R24

1

150R

R24

1

150R

C21

4

47nF

C21

4

47nF

FB205

0R

FB205

0R

C246

0.1uF

C246

0.1uF

R28

9

68R

R28

9

68R

C251

0.1uF

C251

0.1uF

C234

10uF

C234

10uF

MSD3463GSA

U20

1

MSD3463GSA

MSD3463GSA

U20

1

MSD3463GSA

EPAD

217

RX0N_B

1

RX0P_B

2

RX1N_B

3

RX1P_B

4

RX2N_B

5

RX2P_B

6

AVDD_MOD

7

RXCN_A

8

RXCP_A

9

RX0N_A

10

RX0P_A

11

RX1N_A

12

RX1P_A

13

RX2N_A

14

RX2P_A

15

HSYNC0

16

BIN0P

17

GIN0P

18

GIN0M

19

RIN0P

20

VSYNC0

21

AVDD3P3_ADC

22

BIN1P

23

GIN1P

24

GIN1M

25

RIN1P

26

CVBS0

33

CVBS1

34

VCOM

35

CVBS_OUT1

36

VDDC

38

LINEIN_L2

42

LINEIN_R2

43

AUVRM

40

VAG

41

LINEIN_L4

46

LINEIN_R4

47

AVDD_AU33

39

LINEOUTR3

48

LINEOUTL3

49

EARPHONE_OUTL

50

EARPHONE_OUTR

51

AVDD33_EAR

52

QP_S

53

QM_S

54

AVDD3P3_DADC

55

IP

_S

56

IM

_S

57

IFA

GC

_S

58

IFA

GC

_T

59

IP

_T

60

IM

_T

61

AVDD

3P

3_D

MP

LL

62

XIN

63

XOU

T

64

VDDC

66

GP

IO

44/TX

1

67

GP

IO

45/R

X1

68

PW

R_O

N/O

FF

69

GP

IO

48/D

ISE

QC

71

VDDIO_C

MD

73

VDDC

74

AVDD

_M

OD

75

PC

M_R

ESET/E

J_R

STZ

76

PCM

_IR

QA_N

77

PCM

_CD

_N

78

PCM

_REG_

N

79

PC

M_C

E_N

80

PCM

_OE_

N

81

PCM

_W

E_N

82

PCM

_W

AIT_

N

83

PCM

_IORD

_N

84

PCM

_IO

WR

_N

85

PCM

_D

0

86

PCM

_D

1

87

PCM

_D

2

88

PCM

_D

3

89

VDDC

166

PW

M1

165

PW

M0

164

RESET

163

IRIN

162

R_ODD[5]/LVB0-

157

R_ODD[4]/LVB0+

156

AVDD_MOD

155

R_ODD[3]/LVB1-

154

R_ODD[2]/LVB1+

153

R_ODD[1]/LVB2-

152

R_ODD[0]/LVB2+

151

G_ODD[7]/LVB3-

150

G_ODD[6]/LVB3+

149

G_ODD[5]/LVB4-

148

G_ODD[4]/LVB4+

147

G_ODD[3]/LVA0-

146

G_ODD[2]/LVA0+

145

G_ODD[1]/LVA1-

144

G_ODD[0]/LVA1+

143

B_ODD[7]/LVA2-

142

B_ODD[6]/LVA2+

141

B_ODD[5]/LVACLK-

140

B_ODD[4]/

139

B_ODD[3]/LVA3-

138

B_ODD[2]/LVA3+

137

B_ODD[1]/LVA4-

136

B_ODD[0]/LVA4+

135

DP_P0

134

DM_P0

133

DP_P1

132

DM_P1

131

PCM

_A

0

108

RXCP_B

216

RXCN_B

215

RX

2P_D

214

RX

2N

_D

213

RX

1P_D

212

RX

1N

_D

211

RX

0P_D

210

RX

0N

_D

209

RXCP_D

208

RXCN_D

207

VDDC/AVDDL_

DVI

206

ARC

205

AVDD

_5V

204

HOTP

LU

G_A

203

HOTP

LU

G_B

202

HOTP

LU

G_D

201

CEC

200

GND-EFUS

E

195

VDDIO_DRA

M

189

VDDIO_DAT

A

185

AVDD

_M

OD

184

DV

DD_DDR

_D

ATA

183

SAR1

182

SAR0

181

MH

L_D

ET

178

DDCA_C

K

177

DDCA_D

A

176

VDDC

174

SPI_DO

/SP

I-N

AND_DO/N

ANAD_RBZ

173

SPI_CK

/SP

I-N

AND_CK/N

AND_ALE

172

SPI-N

AND

_H

OLDN

/N

AND

_W

EZ

170

SPI_D

I/SPI-N

AND

_D

I/N

AND

_R

EZ

169

VSYNC1

27

BIN2P

28

GIN2P

29

GIN2M

30

RIN2P

31

PANEL_ON/OFF

32

CVBS_OUT2

37

LINEIN_L3

44

LINEIN_R3

45

SPI-NAND

_W

P/NAND

_W

P

171

GP

IO

68/M

HL_

VBS

65

VBL_C

TR

L

70

GPIO49

/I2

S_OU

T_W

S

72

PC

M_D4

/E

J_TC

K

90

PC

M_D5

/E

J_TD

O

91

PC

M_D6

/E

J_TD

I

92

PCM

_D7

/E

J_TRST

N

93

PCM

_A1

4

94

PCM

_A1

3

95

PCM

_A12

/E

J_D

IN

T

96

PCM

_A1

1

97

PCM

_A1

0

98

PCM

_A

9

99

PCM

_A

8

100

PCM

_A

7

101

PCM

_A6

/E

J_T

MS

102

PCM

_A

5

103

PCM

_A

4

104

PCM

_A

3

105

PCM

_A

2

106

PCM

_A

1

107

TS1_D0

130

TS1_D1

129

TS1_D2

128

TS1_D3

127

TS1_D4

126

TS1_D5

125

TS1_D6

124

TS1_D7

123

TS1_VLD

122

TS1_SYNC

121

TS1_CLK

120

TS0_D0

119

TS0_D1

118

TS0_D2

117

TS0_D3

116

TS0_D4

115

TS0_D5

114

TS0_D6

113

TS0_D7

112

TSO_VLD

111

TS0_SYNC

110

TS0_CLK

109

AVDDL_MOD/VDDC

158

GPIO0/TX2/I2S_OUT_MCK

161

GPIO2/RX2/I2S_OUT_BCK

160

GPIO56/I2S_OUT_SD

159

NAND_C

LE

168

SPI_CS

/SP

I-N

AND_CS/N

AND_CEZ

167

GP

IO

96/SP

DIF

_O

UT

175

DDCDD_C

LK

179

DDCDD_SD

A

180

GN

D

186

VDDIO_DAT

A

187

VDDIO_DRA

M

188

AVDD_ETH

190

RN

191

TP

194

TN

193

RP

192

DDCDB_C

LK

197

DDCDB

_DA

T

196

DDCDA_C

LK

199

DDCDA

_DA

T

198

GN

D

218

1K

1K

2T

2T

3C

3C

C249

2.2uF

C249

2.2uF

C291

0.1uF

C291

0.1uF

FB201

150mA/1K

FB201

150mA/1K

C285 2.2uF

C285 2.2uF

C290

0.1uF

C290

0.1uF

R29

9

0R

R29

9

0R

C20

3

47nF

C20

3

47nF

R22

8

0R

R22

8

0R

U204

MX25L6406E

U204

MX25L6406E

CE#

1

SO

2

WP#

3

VSS

4

SI

5

SCK

6

HOLD#

7

VDD

8

C280

0.1uF

C280

0.1uF

C22

1

2.2uF

C22

1

2.2uF

C236

2.2uF

C236

2.2uF

R268

4.7K

R268

4.7K

C254

0.1uF

C254

0.1uF

R55

4.7K

R55

4.7K

C289

0.1uF

C289

0.1uF

TP5TP5

1

C238

0.1uF

C238

0.1uF

C253

0.1uF

C253

0.1uF

C288

0.1uF

C288

0.1uF

C28

4

8pF

C28

4

8pF

C239

0.1uF

C239

0.1uF

C292

0.1uF

C292

0.1uF

R26

6

200R

R26

6

200R

R270

100R

R270

100R

R29

4

33R

R29

4

33R

C243

0.1uF

C243

0.1uF

C279

0.1uF

C279

0.1uF

R28

6

33R

R28

6

33R

C240

0.1uF

C240

0.1uF

C274

2.2uF

C274

2.2uF

R28

5

0R

R28

5

0R

R28

7

33R

R28

7

33R

R25

1

10K/NC

R25

1

10K/NC

R255

10K

R255

10K

TP7TP7

1

C21

1

47nF

C21

1

47nF

C21

3

47nF

C21

3

47nF

C241

0.1uF

C241

0.1uF

C278

0.1uF

C278

0.1uF

R29

6

33R

R29

6

33R

TP8TP8

1

C20

5

47nF

C20

5

47nF

R54

4.7K

R54

4.7K

C20

4

47nF

C20

4

47nF

C250

0.1uF

C250

0.1uF

FB211

100MHZ/300mA/600R

FB211

100MHZ/300mA/600R

C28

1

8pF

C28

1

8pF

R26

4

0R

R26

4

0R

C259

2.2uF

C259

2.2uF

C252

0.1uF

C252

0.1uF

FB202

100MHZ/300mA/600R

FB202

100MHZ/300mA/600R

Y201

24MHZ/8pF

Y201

24MHZ/8pF

1

2

3

C21

6

47nF

C21

6

47nF

C282 0.1uF

C282 0.1uF

C22

0

2.2uF

C22

0

2.2uF

FB209

100MHZ/300mA/600R

FB209

100MHZ/300mA/600R

R269 100K

R269 100K

C277

0.1uF

C277

0.1uF

C244

0.1uF

C244

0.1uF

R104

7

100R

R104

7

100R

FB21

2

0R

FB21

2

0R

FB207

100MHZ/300mA/600R

FB207

100MHZ/300mA/600R

R104

8

100R

R104

8

100R

R271

100R

R271

100R

C262 22nF

C262 22nF

R24

9

10K/NC

R24

9

10K/NC

C245

0.1uF

C245

0.1uF

R24

2

180R

R24

2

180R

R29

5

33R

R29

5

33R

R27

2

1K

R27

2

1K

C21

7

47nF

C21

7

47nF

R22

6

10K

R22

6

10K

R267

4.7K

R267

4.7K

C20

6

47nF

C20

6

47nF

R28

8

33R

R28

8

33R

L32R63_VKE,L40R63_VKE,L43R63_VKE,L49R63_VKE_CIS_Russia.indd 30

2016-04-05 오전 11:01:04