7.Electrical Interface

© China Daheng Group, Inc. Beijing Image Vision Technology Branch 36

Logic 0 input voltage: 0V ~ +2.5V (Line0+ voltage)

Logic 1 input voltage: +5V ~ +24V (Line0+ voltage)

Minimum input current: 7mA

The status is unstable when input voltage is between 2.5V and 5V, which should be avoided

When the external input voltage is 5V, there is no need for circuit-limiting resistance in the external

input. But if there is a series resistance

, please ensure the value is less than 90Ω. In order to protect

the Line0+ while the external input voltage is higher than 9V, a circuit-limiting resistance is needed in

the external input. The recommended resistance is shown in Table 7-3

External input voltage

Circuit-limiting resistance Rlimit

Line0+ input voltage

5V

Non or <90

Ω

About 5V

9V

680Ω

About 5.5V

12V

1kΩ

About 6V

24V

2kΩ

About 10V

Table 7-3 Circuit-limiting resistor value

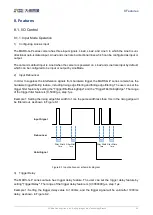

The connection method of the opto-isolated input circuit and the NPN and PNP photosensor is shown in

Figure 7-2 and Figure 7-3. The relationship between the pull-up resistor value and the external power

supply voltage is shown in Table 7-3.

3.3V

Line0+

Line0-

FPGA INPUT0

External circuit

Camera internal circuit

Signal output

Power +

PWR GND

NPN

Pull-up

resistor

9

1

2

3

4

5

6

7

8

12

11

10

Figure 7-2 NPN photosensor connected to opto-isolated input circuit