7.Electrical Interface

© China Daheng Group, Inc. Beijing Image Vision Technology Branch 41

3.3V

Line2

FPGA INPUT2

Camera internal

circuit

External circuit

Signal

output

Power+

PWR

GND

PNP

Pull-down

resistor

9

1

2

3

4

5

6

7

8

12

11

10

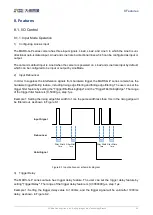

Figure 7-10 PNP photoelectric sensor connected to Line2 input circuit

When Line2/3 is configured as input, if the corresponding output device is common-anode connected, pull-

down resistor over 1K should not be used, otherwise the input voltage of Line2/3 will be over 0.6V and

logic 0 cannot be recognized stably.

Input rising time delay: <

2μs (0°C ~ 45°C), parameter description as shown in Figure 7-4

Input falling time delay: <

2μs (0°C ~ 45°C), parameter description as shown in Figure 7-4

7.3.3.2. Line2/3 is Configured as Output

Range of external voltage (EXVCC) is 5~24V

Maximum output current of Line2/3 is 25mA, output impedance is 40Ω

Output voltage and output current in typical application conditions (temperature is 25

℃

) are shown in Table 7-7

External voltage

EXVCC

External resistance

Rexternal

Line2/3 voltage (V)

Output current (mA)

5V

1kΩ

0.19

4.8

12V

0.46

11.6

24V

0.92

23.1

Table 7-7 Voltage and output current of Line2/3 in typical conditions

Rising time delay = tr+td: <

20μs (0°C ~ 45°C) (parameter description as shown in Figure 7-6)

Falling time delay = ts+tf: <

20μs (0°C ~ 45°C) (parameter description as shown in Figure 7-6)

Delay parameters are affected greatly by external voltage and external pull-up resistor, but little by

temperature. Output delays in typical application conditions (temperature is 25°C) are shown in Table

7-8