D i d o H a r d w a r e M a n u a l

v . 1 . 0 . 5

Connector Pin

Pin

name

Function

Notes

J2.119

7.15

I2C buses

Two I2C channels are available on DIDO to provide an interface

to other devices compliant with Philips Semiconductors Inter-IC

bus (I2C-bus™) specification version 2.1. External components

attached to this 2-wire serial bus can transmit/receive 8-bit

data to/from the device through the I2C module. The I2C ports

support standard and fast modes from 10 - 400 Kbps (no

fail-safe I/O buffers).

A third I2C channel (I2C0) is used for the internal connection

between CPU and PMIC (please refer to Section 5.2).

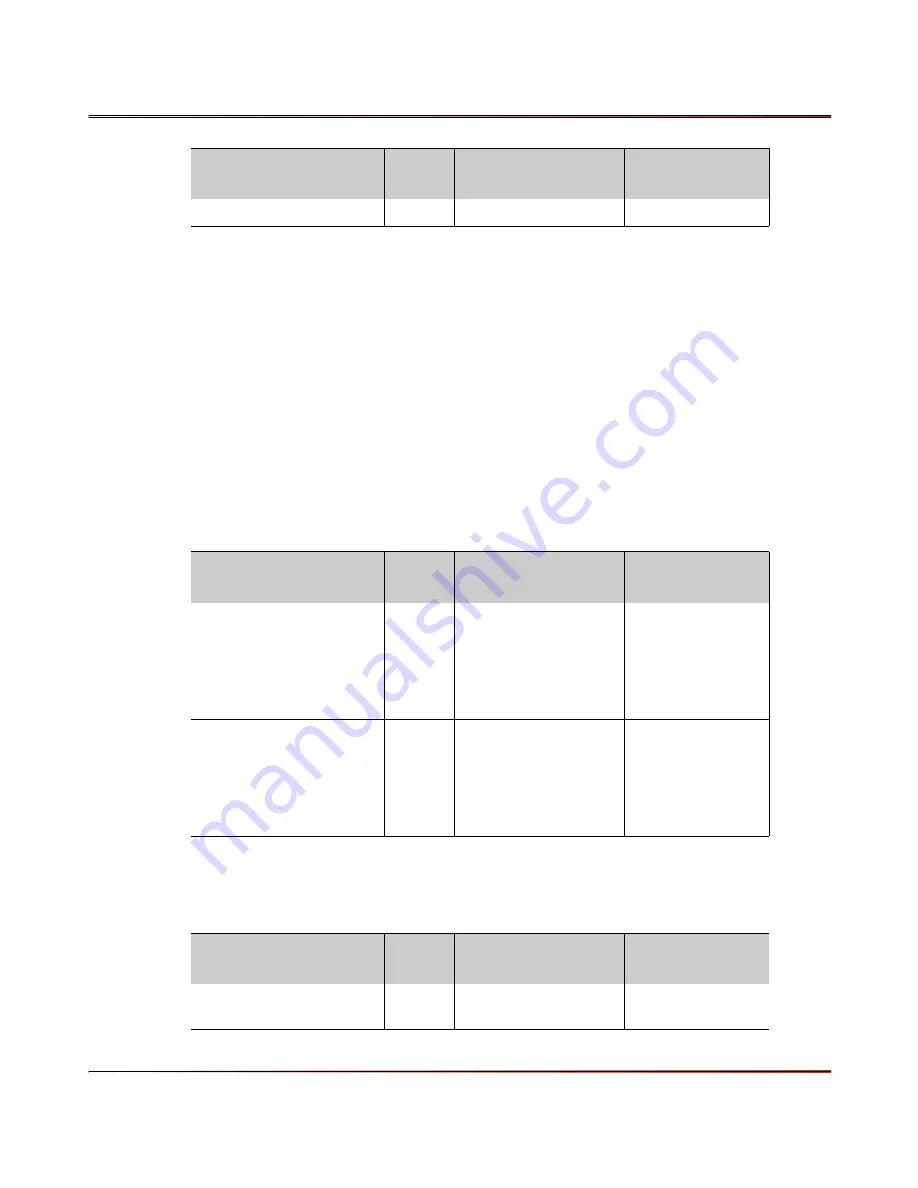

7.15.1 I2C2

The following table describes the interface signals:

Connector Pin

Pin

name

Function

Notes

I2C[2]_SCL

J1.23

J2.122

J2.128

I2C2 Clock

For proper device

operation in I2C

mode, this pin

must be pulled

up via

external resistor.

I2C[2]_SDA

J2.39

J2.66

J2.120

J2.121

I2C2 Data I/O

For proper device

operation in I2C

mode, this pin

must be pulled

up via

external resistor.

7.15.2 I2C3

The following table describes the interface signals:

Connector Pin

Pin

name

Function

Notes

I2C[3]_SCL

J2.106

J1.27

I2C3 Clock

J2.106 line is

internally

August, 2014

69/78