SFBD-155E2J1RM

DELTA ELECTRONICS, INC.

4 Revision:

S0

12/20/2006

www.deltaww.com

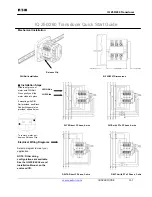

6. Pin Description

Tx/Rx

Pin No.

I/O

Pin Name

Description

1

VeeR

Receiver

Ground

2

VccR

+3.3V Receiver Power Supply

3 O SD

Normal Optical Input indicated by logic “High”, and No Optical

Input indicated by logic “Low”.

4

O

RD(n)

Inverted Receiver Data Output

Rx

5 O

RD(p)

Non-Inverted

Receiver

Data

Output

6

VccT

+3.3V Transmitter Power Supply

7

VeeT

Transmitter

Ground

8 I

Tx_Dis

LVTTL Logic “High” to Disable Transmitter, and Enable

Transmitter by Logic “Low” or “Open”.

9 I

TD(p)

Non-Inverted

Transmitter

Data

Input

Tx

10 I TD(n)

Inverted

Transmitter

Data

Input

MS

Mounting studs/ connect this pin to Chassis ground

Note. EMI shielding lead must be connected to Signal ground

Bottom View

MS

MS