21

DHT-500SD

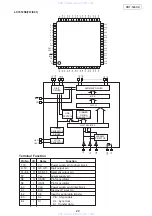

ST92F150CVT1(MAIN:IC11)

Pin Configuration (Top-view TQFP100)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81 80 79 78 77 76

ST92F150CVT1

(MAIN:IC11)

P8.4/AIN4

P8.3/AIN3

P8.2/AIN2

P8.1/AIN1/WKUP15

P8.0/AIN0/WKUP14

NC

P6.5/WKUP10/INTCLK

P6.4/NMI

P6.3/INT3/INT5

P6.2/INT2/INT4/DS2

P6.1/INT6/RW

P6.0/INT0/INT1/CLOCK2/8

P0.7/A7/D7

V

DD

V

SS

P0.6/A6/D6

P0.5/A5/D5

P0.3/A3/D3

P0.2/A2/D2

P0.1/A1/D1

P0.0/A0/D0

AS

DS

P0.4/A4/D4

P1.7/A15

A20/P9.6

TX0/WAIT/WKUP5/P5.0

RX0/WKUP6/WDOUT/P5.1

TXCLK/CLKOUT/P5.4

OCMPA1/P4.2

V

DD

A21/P9.7

WDIN/SOUT/P5.3

DCD/WKUP8/P5.6

V

SS

ICAPB1/OCMPB1/P4.3

SDA/P4.6

SIN/WKUP2/P5.2

RXCLK/WKUP7/P5.5

CLOCK2/P4.1

EXTCLK1/WKUP4/P4.4

ICAPB0/P3.1

ICAPA0/OCMPA0/P3.2

WKUP9/RTS/P5.7

ICAPA1/P4.0

EXTRG/STOUT/P4.5

WKUP1/SCL/P4.7

OCMPB0/P3.3

EXTCLK0/SS/P3.4

MISO/P3.5

P9

.5

/A1

9

P9

.4

/A1

8

P9

.2

/A1

6

HW

0S

W1

P

7

.7

/AIN

1

5

/7

/W

KU

P1

3

P7

.4

/AIN

1

2

/W

KU

P

3

P9

.3

/A1

7

P9

.0

/R

D

I

RE

S

E

T

P7

.6

/AIN

1

4

/W

KU

P

1

2

P7

.5

/AIN

1

3

/W

KU

P

1

1

P7

.1

/AIN

9

P9

.1

/T

D

O

OS

C

IN

V

SS

P7

.3

/AIN

1

1

P7

.0

/AIN

8

/C

K

_

A

F

P8

.7

/AIN

7

O

S

CO

UT

V

DD

P7

.2

/AIN

1

0

AV

SS

AV

DD

P8

.6

/AIN

6

P8

.5

/AIN

5

MO

SI/

P

3

.6

SC

K/W

KU

P

0

/P3

.7

RW

TOU

T

A

0

/P

2

.2

V

SS

*V

TE

S

T

V

RE

G

TI

N

P

B

0

/P

2

.1

TOU

T

B

0

/P

2

.3

V

DD

V

RE

G

A1

0

/P1

.2

TI

N

P

A

0

/P

2

.0

TI

N

P

B

1

/P

2

.5

TOU

T

B

1

/P

2

.7

A8

/P

1

.0

A1

1

/P1

.3

A1

2

/P1

.4

TI

N

P

A

1

/P

2

.4

TOU

T

A

1

/P

2

.6

A9

/P

1

.1

WK

UP

6

NC

A1

3

/P1

.5

A1

4

/P1

.6

* V

TEST

must be kept low in standard operating mode.

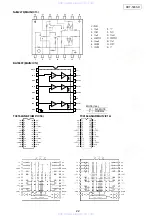

Architectural Block Diagram

256 bytes

Register File

RAM

2/4 Kbytes

8/16 bits

CPU

Interrupt

Management

ME

MOR

Y

BU

S

Ext. MEM.

ADDRESS

DATA

Port0

Ext. MEM.

ADDRESS

Ports

1,9*

RE

GISTE

R

BU

S

WATCHDOG

AS

DS

RW

WAIT

NMI

DS2

RW*

MISO

MOSI

SCK

SS

A[10:8]

A[21:11]*

A[7:0]

D[7:0]

SPI

SDA

SCL

I

2

C BUS

FLASH

128/64 Kbytes

WDOUT

HW0SW1

* Not available on 64-pin version.

Fully

Prog.

I/Os

P0[7:0]

P1[7:3]*

P1[2:0]

P2[7:0]

P3[7:4]

P3[3:1]*

P4[7:4]

P4[3:0]*

P5[7:0]

P6[5:2,0]

P6.1*

P7[7:0]

P8[7:0]*

P9[7:0]*

MF TIMER 0

TINPA0

TOUTA0

TINPB0

TOUTB0

TINPA1

TOUTA1

TINPB1

TOUTB1

INT[5:0]

INT6*

WKUP[13:0]

MF TIMER 1

E

3 TM

1 Kbyte

ADC

AV

DD

AV

SS

AIN[15:8]

AIN[7:0]*

EXTRG

RX0

TX0

CAN_0

V

REG

VOLTAGE

REGULATOR

The alternate functions (Italic characters) are mapped on Port 0, Port 1, Port2, Port3, Port4, Port5, Port6, Port7,

Port8* and Port9*.

OCMPB1

EXTCLK1

EF TIMER 0 *

EF TIMER 1 *

SCI M

TXCLK

RXCLK

SIN

DCD

SOUT

CLKOUT

RTS

SCI A*

RDI

TDO

www. xiaoyu163. com

QQ 376315150

9

9

2

8

9

4

2

9

8

TEL 13942296513

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299