15

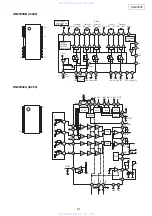

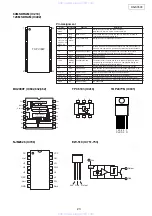

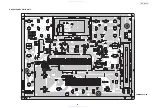

DN-S3500

41

GND

GND

-

-

-

-

-

GND

42

GND

GND

-

-

-

-

-

GND

43

GND

GND

-

-

-

-

-

GND

44

GND

GND

-

-

-

-

-

GND

45

VDDEXT

VDDEXT

I

-

-

-

-

I/O power (+3.3V)

46

PF5

DSPF3

O

-

-

L

-

Programmable flag pin5 Inter micro processor pin3 (RESERVE)

47

PF4

DSPF2

O

-

-

L

-

Programmable flag pin4 Inter micro processor pin2 (RESERVE)

48

PF3

DSPF1

O

-

-

L

-

Programmable flag pin3 Inter micro processor pin1 (RESERVE)

49

PF2

DSPF0

O

-

-

L

-

Programmable flag pin2 Inter micro processor pin0 (RESERVE)

50

PF1

DTIME

O

-

-

L

-

Programmable flag pin1 Clock output for playback

51

PF0

BTEND

O

-

Pd

L

L

Programmable flag pin0 'H' when all boot completed

52

VDDINT

VDDINT

I

-

-

-

-

Internal power (+1.2V)

53

SCK

O

-

-

L

-

Master slave clock

54

MISO

O

-

-

L

-

Master input slave output

55

MOSI

O

-

-

L

-

Master output slave input

56

GND

GND

-

-

-

-

-

GND

57

VDDEXT

VDDEXT

I

-

-

-

-

I/O power (+3.3V)

58

DT1SEC

O

-

-

-

-

Not used

59

DT1PRI

DDATA1

O

-

-

-

-

Main digital out data send 0 (serial port OUT 1)

60

TFS1

DLRCK

I

-

IPu

-

H

Digital out send frame synchro (LRCK) signal (serial port OUT 1)

61

TSCLK1

DBCK

I

-

-

-

-

Digital out send frame synchro (BCK) signal (serial port OUT 1)

62

DR1SEC

I

-

-

L

L

Playback data receive 1

63

DR1PRI

I

-

-

-

-

Not used

64

RFS1

O

-

-

-

-

Not used

65

RSCLK1

O

-

IPu

-

H

Not used

66

VDDINT

VDDINT

I

-

-

-

-

Internal power (+1.2V)

67

DT0SEC

ADATA2

O

-

-

-

-

Not used

68

DT0PRI

ADATA1

O

-

-

-

-

Main analog playback data send 0 (serial port OUT 0)

69

TFS0

ALRCK

I

-

IPu

-

H

Analog playback send frame synchro (LRCK) signal (serial port OUT 0)

70

GND

GND

-

-

-

-

-

GND

71

VDDEXT

VDDEXT

I

-

-

-

-

I/O power (+3.3V)

72

TSCLK0

ABCK

I

-

-

-

-

Analog playback send frame synchro (BCK) signal (serial port OUT 0)

73

DR0SEC

I

-

-

L

L

Playback data receive 1

74

DR0PRI

SRDATA

I

-

-

-

-

Playback data receive 0 (serial port IN 0)

75

RFS0

LRCK

I

-

-

-

-

Receive frame synchro (LRCK) signal (serial port IN 0)

76

RSCLK0

BCLK

I

-

IPu

-

H

Receive frame synchro (BCK) signal (serial port IN 0)

O

-

-

L

-

Timer 2

O

-

-

L

-

Timer 1

O

-

-

L

-

Timer 0

I

-

-

-

-

Internal power (+1.2V)

O

-

Pu

H

-

UART send

I

-

Pu

-

H

UART receive

O

-

-

-

-

Emulation status

I

-

Pd

-

L

Test reset (JTAG)

I

-

Pu

-

H

Test mode select (JTAG)

I

-

Pu

-

H

Test data input (JTAG)

87

TD0

TD0

O

-

-

-

-

Test data output (JTAG)

88

GND

GND

-

-

-

-

-

GND

89

GND

GND

-

-

-

-

-

GND

90

GND

GND

-

-

-

-

-

GND

91

GND

GND

-

-

-

-

-

GND

92

GND

GND

-

-

-

-

-

GND

93

VDDEXT

VDDEXT

I

-

-

-

-

I/O power (+3.3V)

94

TCK

TCK

I

-

Pu

-

H

Test clock (JTAG)

95

BMODE1

BMODE1

I

-

-

-

-

Boot mode strap 1

Pin

No.

Pin Name

Symbol

I/O DET

Ext

Ini

Res

Function

www. xiaoyu163. com

QQ 376315150

9

9

2

8

9

4

2

9

8

TEL 13942296513

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299