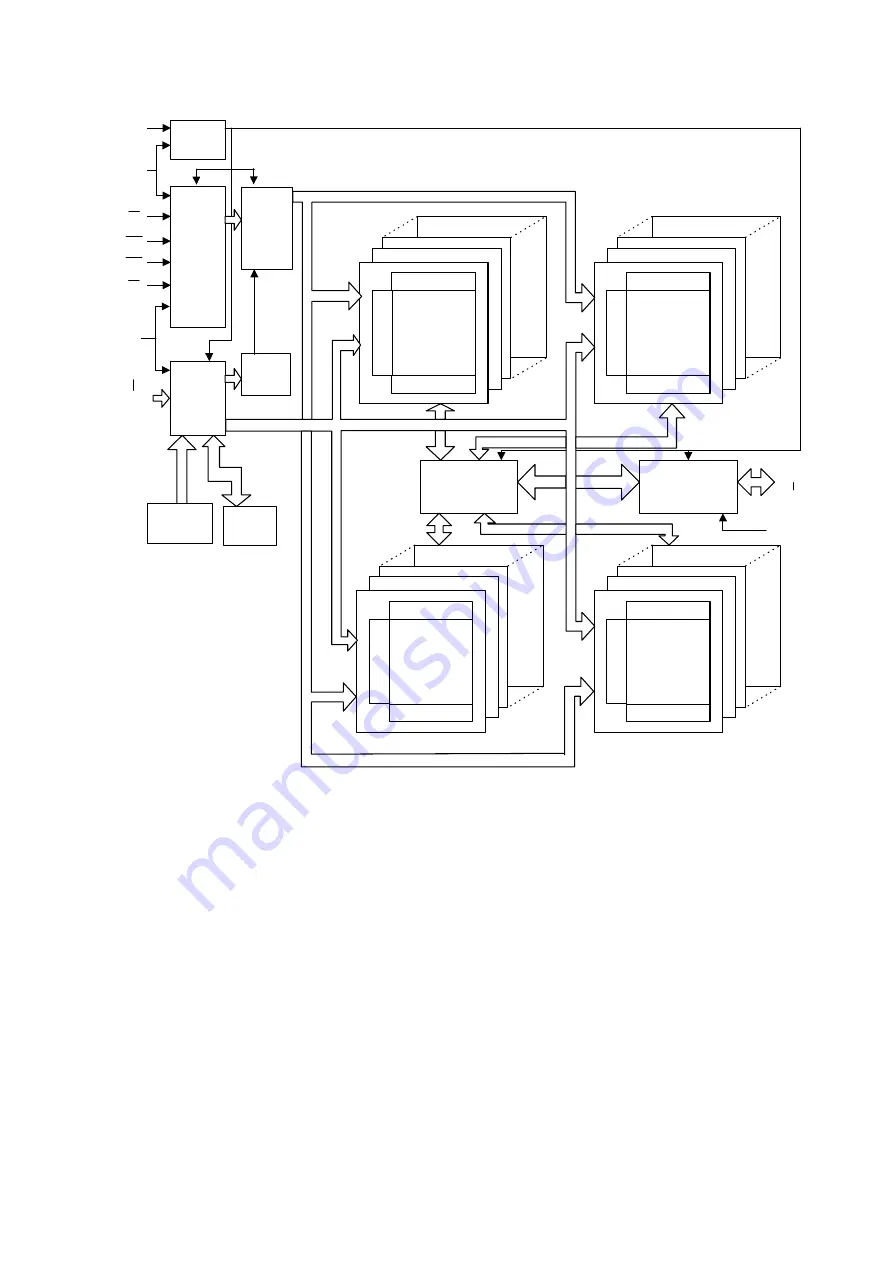

W9864G6JH-6 Block diagram

W9864G2IH

Publication Release Date: Aug. 28, 2009

- 6 -

Revision A03

6. BLOCK DIAGRAM

DQ0

DQ31

DQM0~3

CLK

CKE

A10

CLOCK

BUFFER

COMMAND

DECODER

ADDRESS

BUFFER

REFRESH

COUNTER

COLUMN

COUNTER

CONTROL

SIGNAL

GENERATOR

MODE

REGISTER

COLUMN DECODER

SENSE AMPLIFIER

CELL ARRAY

BANK #2

COLUMN DECODER

SENSE AMPLIFIER

CELL ARRAY

BANK #0

COLUMN DECODER

SENSE AMPLIFIER

CELL ARRAY

BANK #3

DATA CONTROL

CIRCUIT

DQ

BUFFER

COLUMN DECODER

SENSE AMPLIFIER

CELL ARRAY

BANK #1

NOTE:

The cell array configuration is 2048 * 256 * 32

ROW

DE

CODE

R

ROW

DE

CODE

R

ROW

DE

CODE

R

ROW

DE

CODE

R

A0

A9

BS0

BS1

CS

RAS

CAS

WE

177

Summary of Contents for IN-Command AVR-X4000

Page 8: ...Personal notes 8...

Page 19: ...Personal notes 19...

Page 64: ...Personal notes Personal notes 64...

Page 110: ...Personal notes 110...

Page 164: ...Personal notes Personal notes 164...

Page 170: ...R5F3650KNFB DIGITAL IC231 170...

Page 181: ...AK5358BET DIGITAL IC451 AK5358BET Pin Function 181...

Page 194: ...2 FL DISPLAY FLD 17 BT 40GINK FRONT FL601 PIN CONNECTION GRID ASSIGNMENT Y2 q 194...

Page 195: ...ANODE CONNECTION 195...