Hercules-EBX CPU User Manual V1.02

Page 98

This is particularly useful for signals such as the DIOLATCH and EXTTRIG signals, for example,

where a floating input could cause erratic or erroneous results (latch/counter edge trigger could

occur randomly).

To set DIO signal pull-ups or pull-downs, a jumper must be added across signals on header J5,

as indicated here:

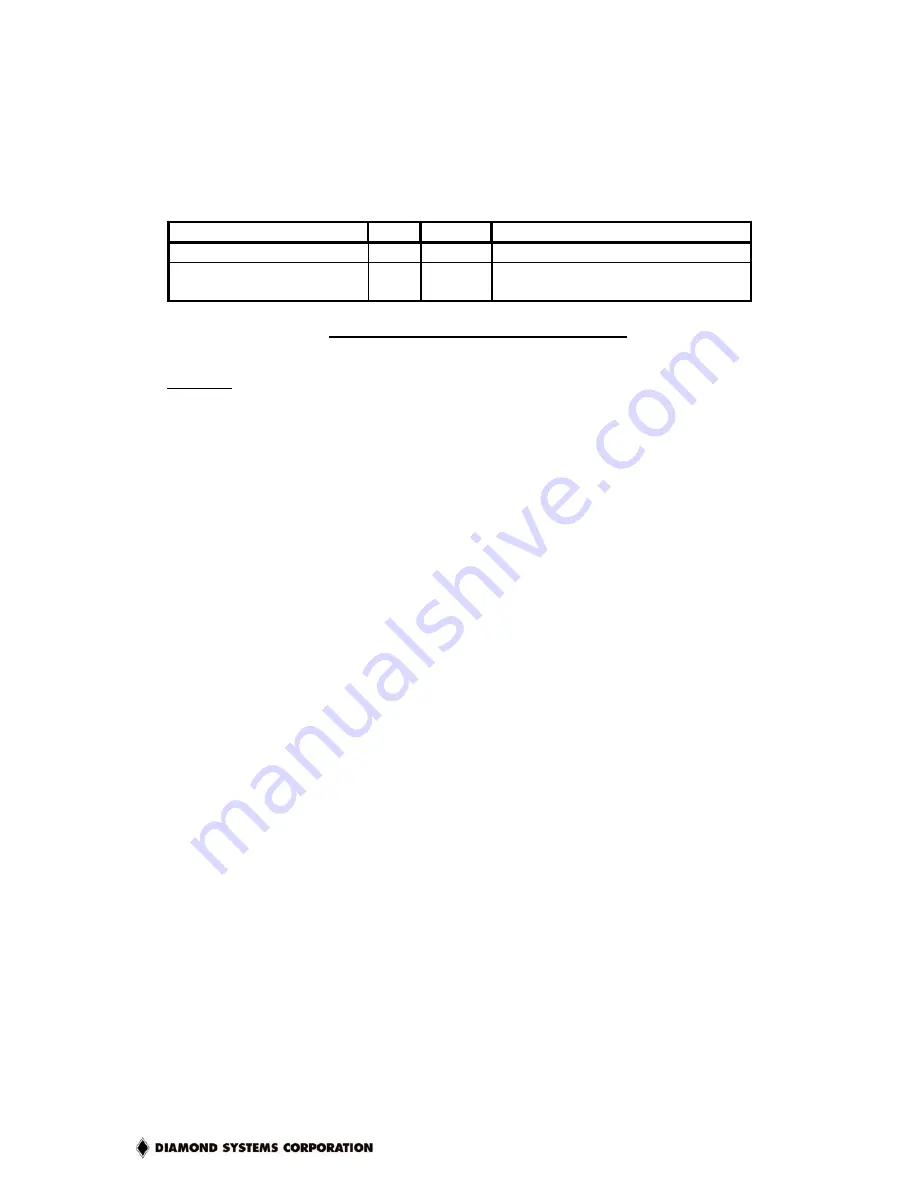

DIO Signal (Range)

Pull-up Pull-down Notes

A7-0, B7-0, C7-0, D7-0, E3-0

1-3

3-5

PWM Outputs are included here

E7-4 (GATE0, TOUT1,

GATE1, DIOLATCH)

2-4

4-6

Affects DIO Hanshaking and GATE for

both Counters

Table 41: DIO Pull-Up/Down Configuration

Note that:

•

“Pull-up” means that a weak (47kOhm) pull-up resistor will be connected between the DIO

signal and +3.3V. This sets the DIO signal to a “1” value when there is no external source

driving the signal.

•

“Pull-down” means that a weak (47kOhm) pull-down resistor will be connected between the

DIO signal and ground. . This sets the DIO signal to a “0” value when there is no external

source driving the signal.

•

FPGA programming / updates: These Pull-up/down resistors also affect signal outputs during

the period when the FPGA is being loaded or re-loaded. During an FPGA update, the FPGA

will briefly tri-state all signals – during this period, the pull-up/down resistors will be the only

current source coming from the board through the DIO signals.

So, for example, to set all standard DIO signals to “0” by default and to allow DIO handshaking to

be configured such that the DIOLATCH signal is pulled high (for normal handshaking operation

default), a jumper would be placed across J5 pins 3-5 (sets normal DIO’s to “0” when not driven)

and across J5 pins 2-4 (sets DIO E7-E4 to “1” when not driven, including “DIOLATCH” which is

present on DIO E6 pin).