The ConnectCore 8X System-on-module

Power interfaces

ConnectCore® 8X System-on-Module Hardware Reference Manual

16

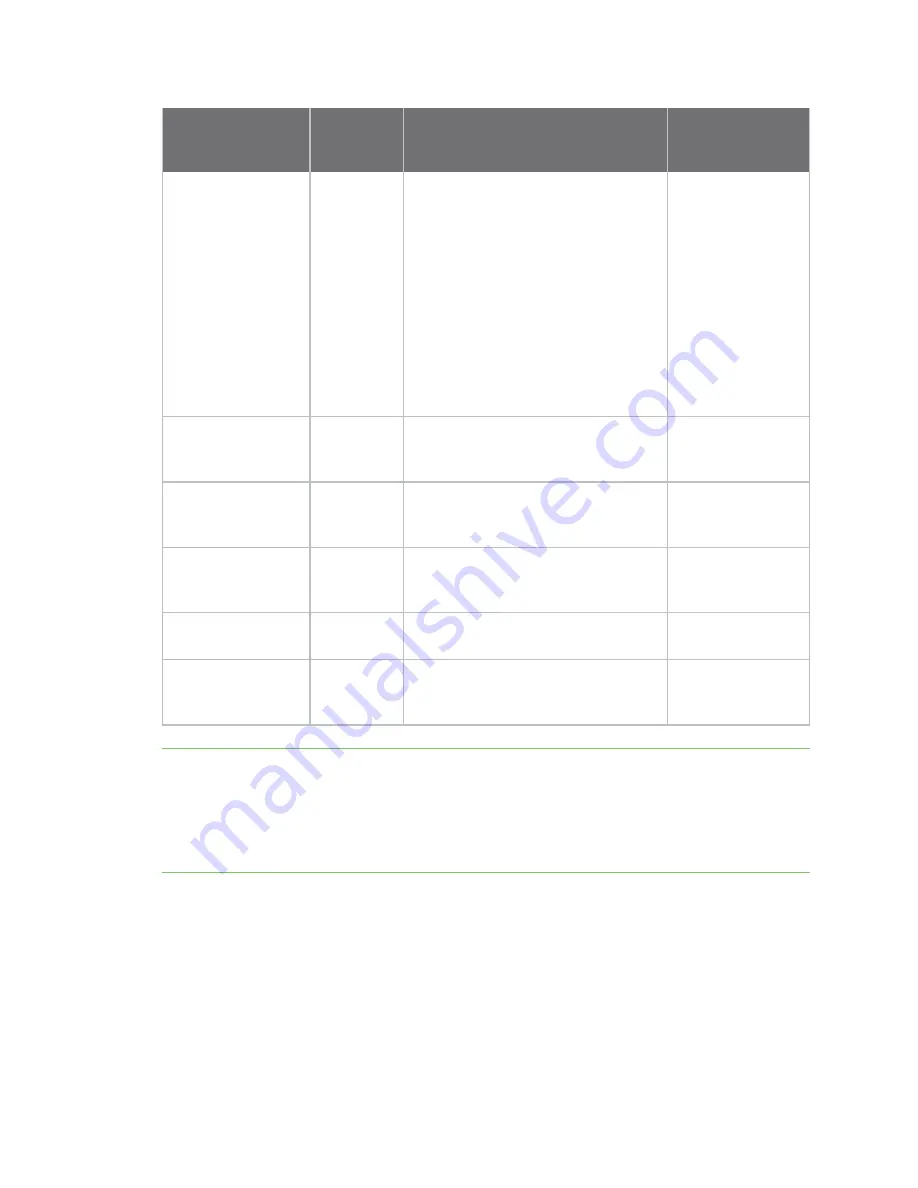

Input rail

Device

being

powered

Internal power domains being

powered

Description

VDD_ENET0

i.MX 8X CPU

n

VDD_ENET0_VSELECT_1P8_2P5_3P3

n

VDD_ENET0_1P8_2P5_3P3

n

VDD_ENET_MDIO_1P8_3P3

Input power supply

for the ENET0

interface, including

the MDIO bus.

Because all ENET0-

related CPU blocks

are powered from

the same power rail,

2.5V configuration is

not available. (The

MDIO bus does not

work at this

voltage.)

VDD_ESAI_SPDIF

i.MX 8X CPU

VDD_ESAI_SPDIF_1P8_2P5_3P3

Input power supply

for ESAI0 and

SPDIF0 interfaces.

VDD_SPI_SAI

i.MX 8X CPU

VDD_SPI_SAI_1P8_3P3

Input power supply

for SAI0, SAI1, SPI0

and SPI2 interfaces.

VDD_QSPI0B

i.MX 8X CPU

VDD_QSPI0B_1P8_3P3

Input power supply

for QSPI0B

interface.

VDD_CSI

i.MX 8X CPU

n

VDD_TMPR_CSI_1P8_3P3

n

VDD_CSI_1P8_3P3

Input power supply

for CSI interface.

USB_OTG1_VBUS

i.MX 8X CPU

USB_OTG1_VBUS

Input power supply

for the USB1

interface VBUS.

Note

The CPU input power rails on the table above power different IO rings (pads) of the processor.

They can remain unconnected and the system will be still functional, as is the case in a castellated

design where some of these supplies are not available. However, the associated pads will remain

unpowered, and therefore not available.

See the

External signals and pin multiplexing

for a complete description of the power group

associated to each pad of the module.

Three additional power domains of the CPU are connected to the module LGA pads, which are

associated in the SOM to the following power rails:

n

VDD_PCIE_DIG: internally tied to 3V3.

n

3V3_RF: internally tied to 3V3.

n

NVCC_MIPI_CSI_DSI: internally tied to 1V8.

Unless otherwise noted, 3V3_RF and NVCC_MIPI_CSI_DSI must not be connected to external circuitry.

In non-wireless variants,

VDD_PCIE_DIG must be powered externally in order to use the PCIe interface.