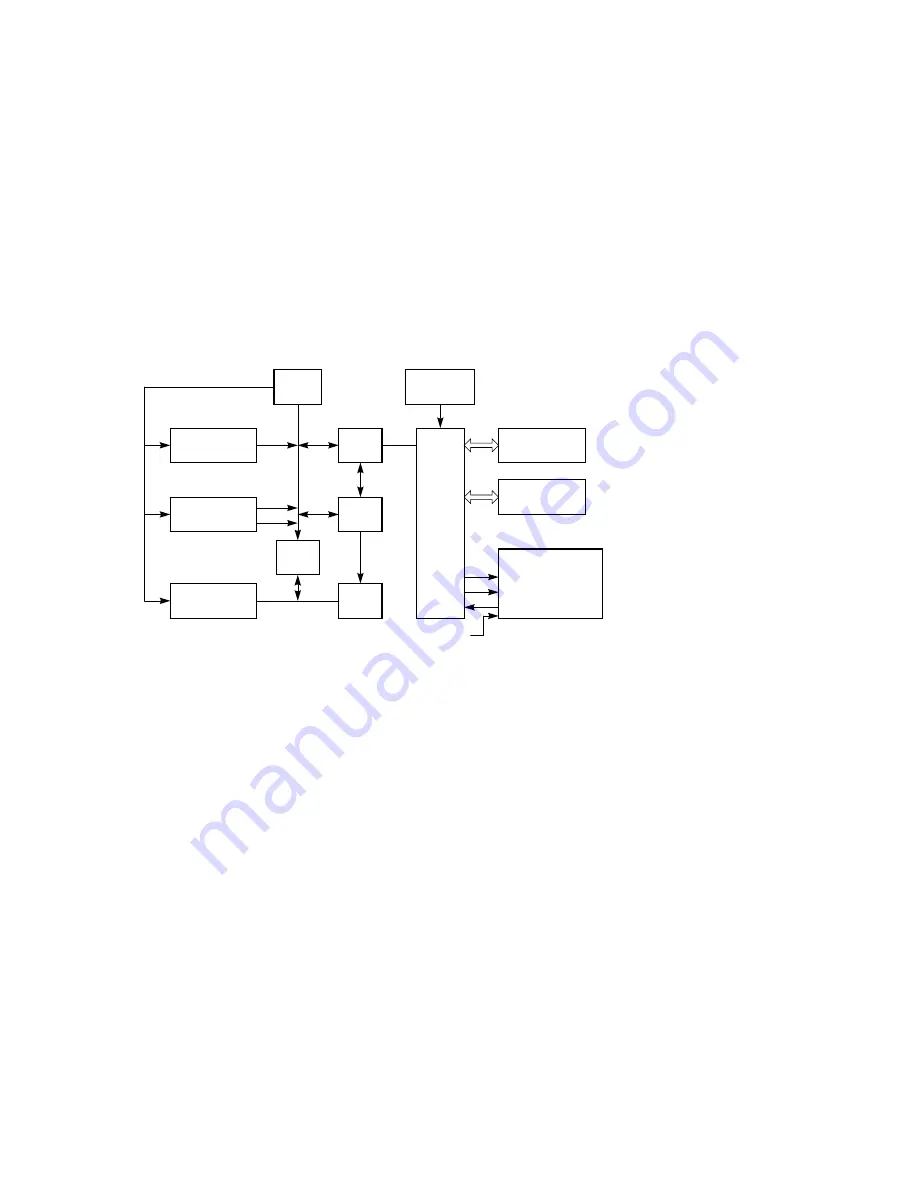

1.7 DEClaser 1100 and 1150 Printer Video Control Board

Figure 1–9 The DEClaser 1100 and 1150 Video Control Board

M-CPU

Expansion

ROM

Font

Cartridges

0

1

Internal

ROM

A16-32

AD0-15

GA2

GA1

DRAM

MD

0-15

EEPROM

S-CPU

I/O

Board

DC Control

Board

Control Panel

Indicators

Display

Keys

MD0-15

MLO-004912

The main central processing unit (M–CPU) is a 32-bit microprocessor that

controls all activity on the video control board.

The subcentral processing unit (S–CPU) is a 16-bit microprocessor that

operates as a slave to the M–CPU. The S–CPU does the following:

• Controls the host system and video control board communication through

the logic elements on the interface board.

• Reads and operates the keys, display, and all indicators on the control

panel.

• Controls read/write access to the electrically erasable programmable

read-only memory (EEPROM). The EEPROM is referred to as NVRAM by

the control panel display (nonvolatile random-access memory).

• Operates the DC control board.

Gate array 1 (GA1) controls the direct memory access (DMA) process to the

DRAM. The DRAM is accessed by the DC control board and by devices on the

video control boards.

Gate array 2 (GA2) controls the transfer timing of the dot pattern data to the

DC control board.

Physical and Functional Description 1–17