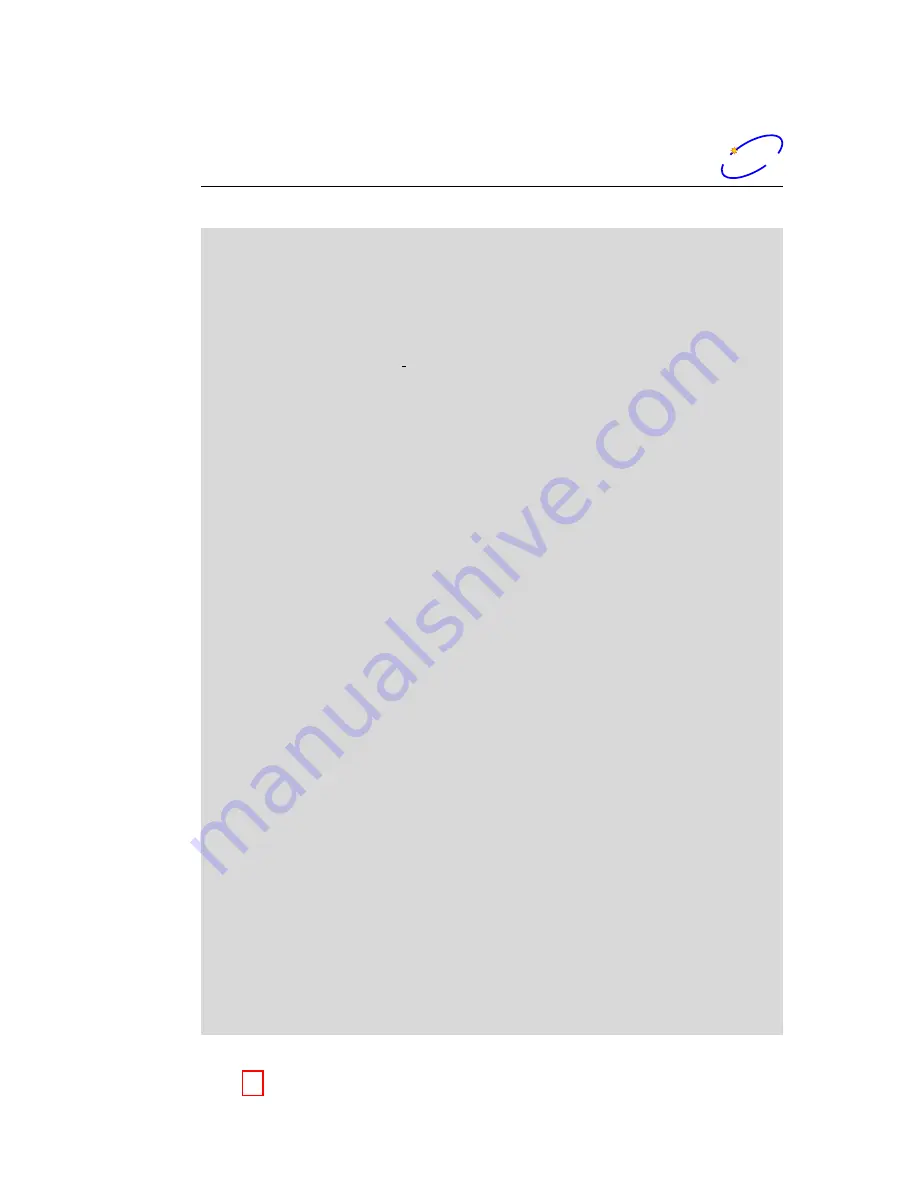

4.2

Selftest

dimtel

dimtel

1 T e r m i n a t i n g t h e IOC

2

3 System i n f o r m a t i o n :

4

F u n c t i o n :

f e e d b a c k

5

Harmonic number : 64

6

D e m u l t i p l e x i n g :

4

7

R e v i s i o n :

1 . 0 1

8

S e r i a l number :

i G p 0 0 0 3

9

10

STARTING THE AUTOMATED TEST SEQUENCE

11

12 T e s t i n g i n t e r n a l blockRAM :

[OK]

13 T e s t i n g e x t e r n a l SRAM:

[OK]

14 T e s t i n g g e n e r a l

−

p u r p o s e d i g i t a l

i n p u t s / o u t p u t s :

[OK]

15 V e r i f y i n g RF c l o c k p r e s e n c e and DCM l o c k :

[OK]

16

17 T e s t i n g low

−

s p e e d DAC/ADC s yste m

18 Ch(ADC) ADC(mV) DAC(mV) O f f (mV) DAC(mV) ADC(mV)

19 1

−

2040

−

2062

5

2039

2025

20 2

−

2024

−

2039

−

4

2039

2028

21 3

−

2035

−

2039

−

3

2039

2033

22 4

−

2029

−

2039

2

2039

2035

23 5

−

2025

−

2039

8

2039

2030

24 6

−

2033

−

2039

−

3

2039

2034

25 7

−

2031

−

2039

−

3

2039

2035

26

27 T e s t i n g high

−

s p e e d DAC o f f s e t

c h a n n e l

28 O f f s e t DAC( c n t ) F a s t ADC( c n t )

29

−

128

−

17.3

30

66

1 . 0

31

127

6 . 9

32

33 T e s t i n g high

−

s p e e d DAC o u t p u t

34 HS DAC( c n t )

HS ADC( c n t )

35

−

1574

−

120.0

36

0

−

0.0

37

1576

1 2 0 . 0

38

39 E n v i r o n m e n t a l measurements

40 Bulk s u p p l y v o l t a g e ( 1 2V ) :

1 2 . 0

41 Vcc s u p p l y v o l t a g e ( 3 . 3V ) :

3 . 3

42 FPGA c o r e s u p p l y v o l t a g e ( 1 . 5V ) :

1 . 5

43 iGp board t e m p e r a t u r e ( deg C ) :

2 5 . 7

44 ADC t e m p e r a t u r e r i s e ( deg C ) :

5 0 . 4

45 FPGA t e m p e r a t u r e r i s e ( deg C ) :

−

0.3

14 of 58