dimtel

dimtel

5.3

Display Panels

5.3.3

Coefficients Panel

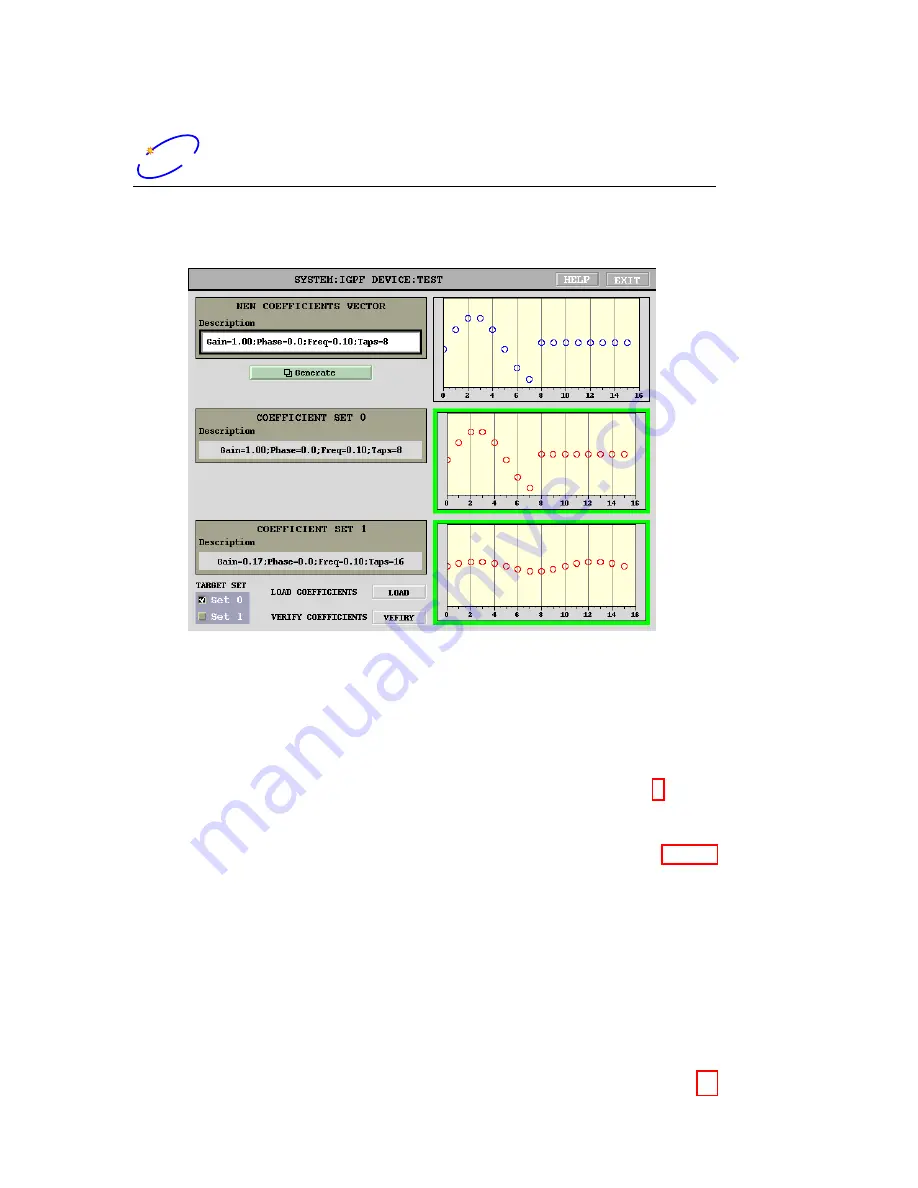

Figure 7: Coefficients panel

Coefficients control panel allows the user to manipulate the loaded coef-

ficients sets and verify that the hardware is in sync with the panel display.

The panel is split into three functional groups: new coefficients vector, coef-

ficient set 0, and coefficient set 1. The first group shows the coefficient vector

and its description generated using coefficient generator panel (Fig. 8). This

vector can be loaded into hardware coefficient sets 0 or 1. Colored borders

around the hardware coefficient displays indicate the results of coefficient

verification. Green shows that the readback is in agreement with the EPICS

values.

Generate

Opens the coefficient generator panel.

TARGET SET

Selects which set the new coefficient vector is to be loaded.

LOAD COEFFICIENTS

Loads the new vector to the hardware coeffi-

cient set specified by

TARGET SET

.

VERIFY

Verifies coefficient sets 0 and 1 against hardware values.

21 of 58