dimtel

dimtel

9.1

Registers

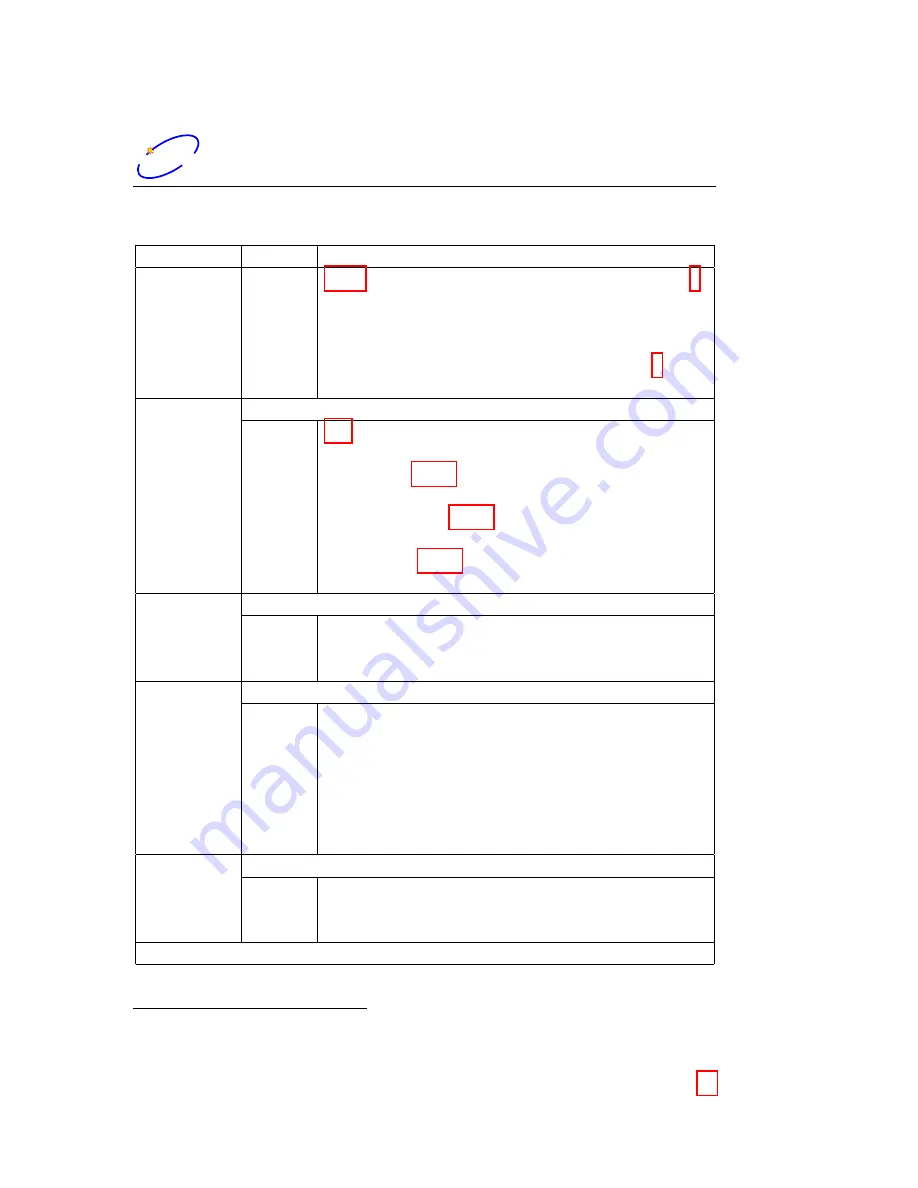

Table 10 – continued from previous page

Address

Bits

Definition

13

DAC drive phase: 0 - 0 degrees, 1 - 180 degrees

14

Turn-by-turn mode of the arbitrary waveform gen-

erator

2

15

Arbitrary waveform generator enable

2

16

GPIO driver select, 0 - bit-by-bit, 1 - FBE

31-17

Reserved

0x000101

Status register, reset on read

0

RF clock missing

1

Saturation

2

Processing DCM unlocked

3

External trigger arming status

4

Local bus clock DCM unlocked

5

Fiducial error

6

Acquisition DCM unlocked

31:7

Reserved

0x000102

DCM phase shift register

8:0

Phase

shift,

default

0x100

(0

deg),

range

0x80(

−

π

) to 0x180 (

π

)

31:9

Unused, read out as 0

0x000104

Output delay length

9:0

Delay length in units of 4 samples

10

Reserved

15:11

Recording downsampling, 0 - every turn,

N

ds

=

1

20:16

Processing downsampling

26:24

Fine delay adjustment, one sample per step

31:27

Reserved

0x000105

Grow/damp filter 2 length

20:0

Number of samples to hold

setsel

inverted during

data acquisition (growth length)

31:21

Reserved

Continued on next page

2

Gateware revision 1.3 and higher

3

Gateware revision 1.4 and higher

43 of 58