9.2

Drive pattern memory

dimtel

dimtel

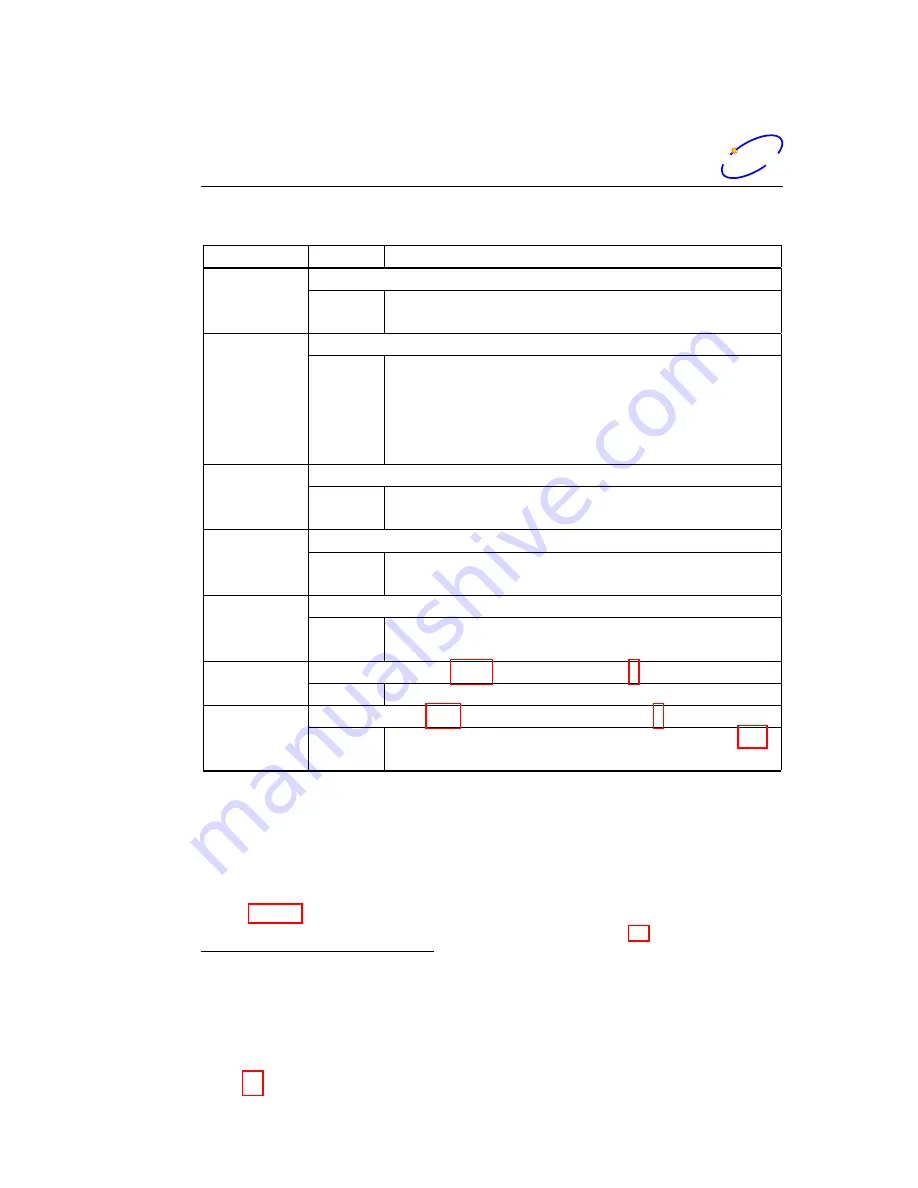

Table 10 – continued from previous page

Address

Bits

Definition

0x000106

Hold-off length

31:0

Number of samples to hold

setsel

inverted before

data acquisition

0x000107

Gateware config register (read-only)

12:0

Harmonic number

14:13

Demux mode, 0 - by4, 1 - by6, 2 - by8, 3 - reserved

15

Reserved

23:16

Gateware revision

31:24

Gateware functionality, 0 - feedback

0x000108

Fiducial delay

11:0

Fiducial delay, two samples per step

31:12

Reserved

0x000109

Acquisition length

20:0

Acquisition length in units of 4 samples

31:21

Reserved

0x000200

Acquisition status (read-only)

0

Acquisition in progress, memory busy

31:2

Reserved

0x000201

31:0

Test pattern start value

0x000202

31:0

Decimated input average, direct current (DC)

gain of 15

.

625

×

10

6

9.2

Drive pattern memory

An arbitrary waveform generator with bunch-by-bunch masking is integrated

in the FPGA gateware. The generator uses two memory blocks to define the

waveform and the bunch mask as documented in Table 11.

4

Gateware revision 1.2 and higher

5

Gateware revision 1.4 and higher

44 of 58