14

STRAP_4

STRAP_8

STRAP_14

STRAP_19

STRAP_8

STRAP_4

STRAP_18

CH0N

CH0_N

.

C8

2.2UF

VREF

.

BC90

NC/100NF

.

BC89

NC/100NF

.

BC82

100NF

.

BC81

100NF

.

BC94

N

C

/100N

F

.

BC9

100NF

.

BC92

NC/100NF

.

BC72

100NF

.

BC95

NC/100NF

.

BC91

NC/100NF

.

BC75

100NF

VDDO

.

BC85

100NF

+

EC2

100UF/16V

.

BC53

100NF

.

BC73

100NF

.

BC71

100NF

.

BC93

NC/100NF

.

BC

N

C

/100N

F

place on bottom layer

,

close to DDR/0603

place on Top layer

,

close to DDR/0402

.

BC76

100NF

.

BC87

4.7UF

.

BC80

100NF

.

R34

1K

.

R16

470R

.

BC79

100NF

.

R40

1K/1%

.

R33

10K

.

BC77

100NF

.

R35

10K

.

BC88

4.7UF

.

R38

1K/1%

NT5TU32M16DG-BE

U5

VDD

A1

NC

A2

VSS

A3

VSSQ

A7

UDQS

A8

VDDQ

A9

DQ14

B1

VSSQ

B2

UDM

B3

UDQS

B7

VSSQ

B8

DQ15

B9

VDDQ

C1

DQ9

C2

VDDQ

C3

VDDQ

C7

DQ8

C8

VDDQ

C9

DQ12

D1

VSSQ

D2

DQ11

D3

DQ10

D7

VSSQ

D8

DQ13

D9

VDD

E1

NC

E2

VSS

E3

VSSQ

E7

LDQS

E8

VDDQ

E9

DQ6

F1

VSSQ

F2

LDM

F3

LDQS

F7

VSSQ

F8

DQ7

F9

VDDQ

G1

DQ1

G2

VDDQ

G3

VDDQ

G7

DQ0

G8

VDDQ

G9

DQ4

H1

VSSQ

H2

DQ3

H3

DQ2

H7

VSSQ

H8

DQ5

H9

VDDL

J1

VREF

J2

VSS

J3

VSSDL

J7

CK

J8

VDD

J9

CKE

K2

WE

K3

RAS

K7

CK

K8

ODT

K9

NC,BA2

L1

BA0

L2

BA1

L3

CAS

L7

CS

L8

A10/AP

M2

A1

M3

A2

M7

A0

M8

VDD

M9

VSS

N1

A3

N2

A5

N3

A6

N7

A4

N8

A7

P2

A9

P3

A11

P7

A8

P8

VSS

P9

VDD

R1

A12

R2

NC,A14

R3

NC,A15

R7

NC,A13

R8

VDDO

DDRII_DQS[0..1]

VDDO

VDDO

DDRII_CK

DDRII_CKJ

DDRII_DQ[0..15]

DDRII_WEJ

DDRII_CASJ

DDRII_A[0..12]

VREF

DDRII_DQM[0..1]

DDRII_RASJ

DDRII_BA[0..2]

DDRII_CKE

(1066)

DDRII_DQSJ[0..1]

DDRII_CK

DDR II

DDRII_ODT

DDRII_BA[0..2]

DDRII_DQSJ[0..1]

DDRII_DQS[0..1]

DDRII_CKJ

DDRII_DQM[0..1]

DDRII_WEJ

DDRII_CKJ

DDRII_CSJ

CLKN

CLK_N

DDR

DDRII_A[0..12]

DDRII_RASJ

DDRII_DQ[0..15]

DDRII_CASJ

VREF

DDRII_CK

DDRII_DQ15

DDRII_DQ11

DDRII_DQ8

DDRII_DQ5

DDRII_DQ2

DDRII_DQ14

DDRII_BA0

DDRII_DQ3

DDRII_DQ10

DDRII_DQ9

DDRII_DQ6

DDRII_DQSJ0

DDRII_DQM1

DDRII_DQ13

DDRII_DQ12

DDRII_BA2

DDRII_DQ0

DDRII_DQ4

DDRII_DQ1

DDRII_DQM0

DDRII_DQSJ1

DDRII_DQ7

DDRII_BA1

DDRII_A2

DDRII_A2

DDRII_A11

DDRII_A11

DDRII_DQS0

DDRII_A0

DDRII_A0

DDRII_WEJ

DDRII_DQS1

DDRII_A6

DDRII_A6

DDRII_A10

DDRII_A10

VREF

DDRII_A8

DDRII_A8

DDRII_A5

DDRII_A5

DDRII_CASJ

DDRII_A7

DDRII_A7

DDRII_A4

DDRII_A4

DDRII_A12

DDRII_A12

DDRII_A1

DDRII_A1

DDR II

DDRII_A9

DDRII_A9

DDRII_RASJ

DDRII_A3

DDRII_A3

STRAP[14] _EROM_Enable

0: EROM_disable

1: EROM_Enable (default)

STRAP[8] _CPU_CLK_SEL

{XSF_SCLK}

0,675MHz;(default)

STRAP[18] _SF_Boot Enable

{XSF_MOSI}

0: Sflash boot (default)

STRAP[19] _CPU Probe En

0: Probe disable(Default)

1: Probe enable

STRAP[4] _DRAM clock selection

{XSF_MISO}

0: 528M(default)

USB_5V

.

R39

1.8K

E3

CS0806S

1

1

10

10

2

2

9

9

4

4

7

7

5

5

6

6

3

3

8

8

.

R41

1.8K

.

R43

1.4K/NC

.

BC67

100NF

.

R45

33R

.

R20

4.7K

.

R25

4.7K

USBPWR0

E2

CS0806S

1

1

10

10

2

2

9

9

4

4

7

7

5

5

6

6

3

3

8

8

.

R17

4.7K

J2

HDMI

DETECT

19

+5V

18

GND

17

SDA

16

SCL

15

NC.

14

CEC

13

CLOCK-

12

GND

11

CLOCK+

10

DATA_0-

9

GND

8

7

DATA_1-

6

GND

5

4

DATA_2-

3

GND

2

1

GN

D

20

GN

D

21

GN

D

22

GN

D

23

.

R18

30K

E6

CS0801S

1

1

2

2

J1

USB1(A TY PE)

5V

1

DM

2

DP

3

GND

4

G1

5

G2

6

.

R46

0R

STRAP94

[4,5]

STRAP94

STRAP94

.

R50

4.7K

.

R48

NC/4.7K

.

R47

10K

.

R21

4.7K

E5

CS0801S

1

1

2

2

SF_SCK

.

R30

4.7K

.

R29

4.7K

.

BC46

100NF

.

R64

4.7K

.

R44

33R

U3

GD25Q32BSIG

CS#

1

SO

2

W#

3

GND

4

SI

5

SCK

6

HOLD#

7

VCC

8

.

R23

4.7K

STD3V3

SF_SI

SF_SO

SF_WJ

SF_HOLDJ

JP1

1

2

.

R19

NC/4.7K

CK1

NC/COMMOM CHOKE

1

1

2

2

4

4

3

3

SF_CS

.

R15

NC/4.7K

HDMI5V

STD3V3

EDDC_SDA

[3]

CH2_P

[3]

CLK_N

[3]

CH2_N

[3]

HTPLG

[3]

EDDC_SCL

[3]

CH0_N

[3]

CLK_P

CLKP

CH0_P

[3]

CLK_P

[3]

CH1_P

[3]

CEC

[3]

CH1_N

[3]

USB2.0_DP0

[3]

USB2.0_DM0

[3]

EDDC_SCL

EDDC_SDA

CH2P

CH2_P

CH2_N

CH2N

STRAP_14

[3,6]

STRAP_19

[3,6]

STRAP_8

[3,5]

STRAP_4

[3,5]

STRAP_18

[3,5]

CH1_N

CH2_N

CH1_P

HTPLG

CLK_P

CH2_P

CH0_P

CEC

HTPLG

EDDC_SDA

CLK_N

EDDC_SCL

CH0_N

CH0P

CH0_P

CH1P

CH1_P

CH1N

CH1_N

C

LKN

C

H

0N

D_HTPLG

C

LKP

CEC

C

H

1P

C

H

2P

C

H

1N

C

H

0P

C

H

2N

USB0-DT

.

R49

0R

.

R68

0R

L34

NC/FB60R/0805

F_STANDBY

STD5V

USB_5V

C73

0.1uF

R92

47K

R69

47K

+

C67

220uF/10V

R74

100R

C10

0.1uF

C22

0.1uF

SF_SO

[3,5]

SF_SCK

[3,5]

SF_SCK

U17

SY 6288A

OUT

1

GN

D

2

OCB

3

EN

4

IN

5

SF_SI

[3,5]

SF_CS

[3]

SF_SI

SF_CS

SF_SO

USB2.0_DP0-DT

USB2.0_DP0

USB 0

JUMPER2

不插

为

L

CPU_PROBE_EN:default L

STRAP_18

STRAP_19

STRAP_14

Strap_Pin

STRAP[94] _SF_work mode

{XGPIO_8}

0:Normal

Receptacle

HDMI

USB2.0_DM0-DT

USB2.0_DM0

SFLASH

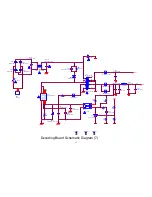

Decoding Board Schematic Diagram (2)

Summary of Contents for SMP012HDT2

Page 6: ...6 Mechanical Exploded View Drawing ...

Page 8: ...8 Packaging and Accessories ...

Page 10: ...10 ...

Page 11: ...11 ...

Page 12: ...12 Flowchart Wiring Diagram ...

Page 20: ...20 ...

Page 22: ...22 Silkscreen of Decoding Board Top ...

Page 23: ...23 Silkscreen of Decoding Board Bottom ...

Page 24: ...24 PCB Diagram of Decoding Board Top ...

Page 25: ...25 PCB Diagram of Decoding Board Bottom ...

Page 33: ...33 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 ...