T5L_ASIC Development Guide

- 5 -

www.dwin-global.com

DWIN Technology

Professional,

Creditable,

S

uccessful

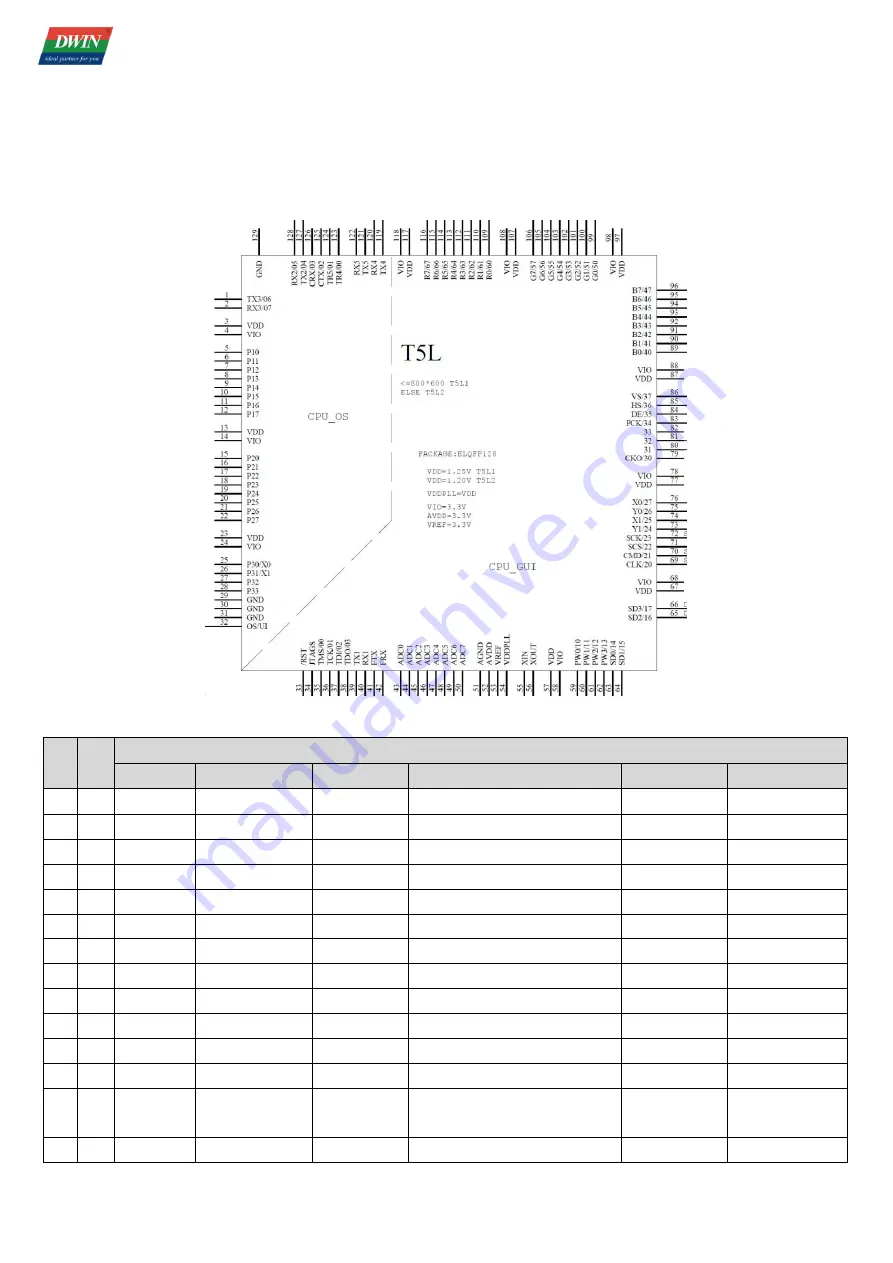

2 Hardware Description

2.1 PIN Definition

T5L ASIC is packaged in ELQFP128 (16*16*1.5mm), and pins arrangement are shown below.

T5L pin

CPU PIN#

Definition

Function 1

Instructions

Function 2

Instructions

Function 3

Instructions

OS

119

TX4

UART4 data

sending

OS

120

RX4

UART4 data

receiving

OS

121

TX5

UART5 data

sending

OS

122

RX5

UART5 data

receiving

OS

123

P0.0

I/O port

OS

124

P0.1

I/O port

OS

125

P0.2

I/O port

CAN_TX

CAN data sending

OS

126

P0.3

I/O port

CAN_RX

CAN data receiving

OS

127

P0.4

I/O port

TX2

UART2 data sending

OS

128

P0.5

I/O port

RX2

UART2 data receiving

OS

1

P0.6

I/O port

TX3

UART3 data sending

OS

2

P0.7

I/O port

RX3

UART3 data receiving

OS

3

VDD

T5L1=1.25V

T5L2=1.2V

OS

4

VIO

3.3V