IL17569

Page 9-4

Effective June, 2001

9.2.1 Relay Test

The FP-5000 has provisions for testing the output relays

individually or as a group. From the front panel Test menu, use the

Operate Relays and Reset Relays menu functions to energize and

de-energize the relays. The same functionality is provided via the

communication interface. When a relay is energized using the Relay

Test function, it will remain energized until it is de-energized through

the Reset menu, Test menu or Remote Reset.

9.2.2 Disarm Trip

The FP-5000 relay can be disarmed to prevent operation of the Trip

1 and Trip 2 output relays during testing. When the Disarm Control

System Configuration setting is Enabled (activated by the “Set”

pushbutton), the user can Disarm tripping using the Test menu Arm/

Disarm Trip function (activated by the “Test” pushbutton). The Relay

Healthy Alarm is de-energized when tripping is disarmed.

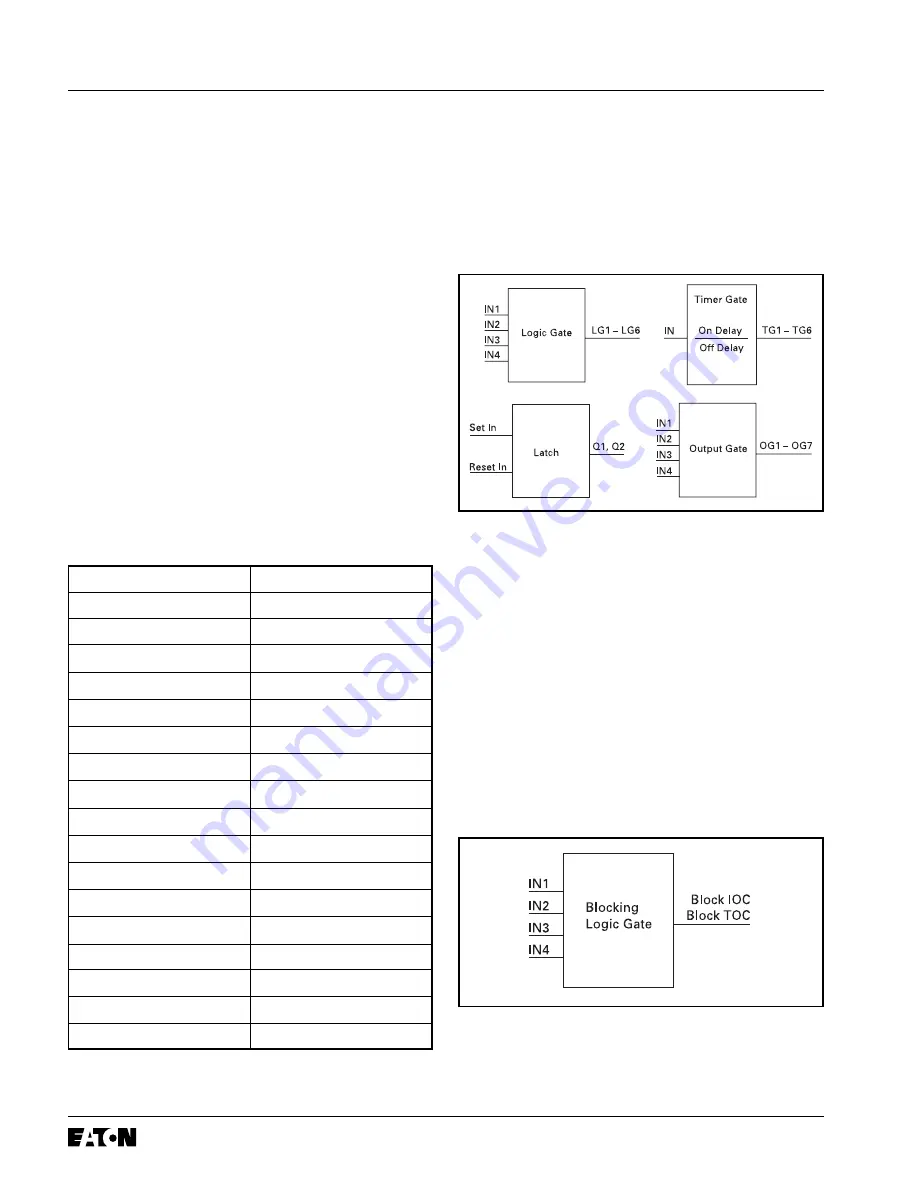

9.3 Programmable Logic Elements

The FP-5000 provides programmable logic for programming custom

functions. The Programmable Logic functions include 12 blocking

gates for the overcurrent protective functions, six logic gates, six

timer gates, two latches, and seven output gates. The basic logic

element for the blocking gates, logic gates, and output gates is a 4-

input logic gate that can be configured as Disabled, or as an AND,

OR, NAND, or NOR function. Each logic gate accepts up to four

inputs, which can be entered directly or negated. The following table

shows the output of each function for any combination of inputs.

Table 9.3 Logic Functions

Inputs

Outputs

IN1

IN2

IN3

IN4

OR

AND

NOR

NAND

0

0

0

0

0

0

1

1

0

0

0

1

1

0

0

1

0

0

1

0

1

0

0

1

0

0

1

1

1

0

0

1

0

1

0

0

1

0

0

1

0

1

0

1

1

0

0

1

0

1

1

0

1

0

0

1

0

1

1

1

1

0

0

1

1

0

0

0

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

0

1

1

0

1

1

1

0

0

1

1

1

0

0

1

0

0

1

1

1

0

1

1

0

0

1

1

1

1

0

1

0

0

1

1

1

1

1

1

1

0

0

Figure 9-3. Programmable Logic Elements

The default settings for the input and output functions are defined in

the previous sections. The default settings for the remaining logic

functions are disabled or unused. User Defined logic may only be

entered under the Set Mode if the “Prog Logic” setting in the

System Configuration menu is changed from Default to Custom.

If a diagnostic failure is detected, the protective functions and

logic functions are disabled and the Relay Healthy Alarm relay is

de-energized. The other relays will not change state.

9.4 Trip and Alarm Blocking

The FP-5000 has blocking logic functions to block operation of the

overcurrent protective functions. A Blocking logic gate is provided

for each of the nine instantaneous overcurrent and three inverse-

time overcurrent protective functions. They are: 50X-1, 50X-2, 50X-

3, 50R-1, 50R-2, 50R-3, 50P-1, 50P-2, 50P-3, 51P, 51R, 51X. Each

logic gate can be configured as Disabled or as an AND, OR, NAND,

or NOR function. Each logic gate accepts up to four inputs, which

can be entered directly or negated.

A programmable logic gate or timer gate output may be connected

to other timer or logic gates, used to trigger waveform capture

(Logic Gate 6), or tied to an output gate to control an output relay.

Figure 9-4. Blocking Logic Gate

Each timer gate has a single input and a single output with internal

on-delay and off-delay timers. The setting range on the timers is 0

to 9999 cycles with 1-cycle resolution. The latches include a set input

and a reset input. The reset input has the highest priority. If both the

set and reset inputs are active, the latch output is inactive. A diagram

of each logic gate is shown in

Figure 9-3

Programmable Logic Elements.

Summary of Contents for Cutler-Hammer FP-5000

Page 1: ...IL17569 Effective June 2001 Instructions for FP 5000 Protective Relay...

Page 7: ...IL17569 Table of Contents 6 Effective June 2001 This page left blank intentionally...

Page 13: ...IL17569 Page 2 2 Effective June 2001 Figure 2 2 FP 5000 Simple Wye Connected Application...

Page 14: ...Page 2 3 IL17569 Effective June 2001 Figure 2 3 FP 5000 Simple Open Delta Application...

Page 19: ...IL17569 Page 2 8 Effective June 2001 This page left blank intentionally...

Page 25: ...IL17569 Page 3 6 Effective June 2001 This page left blank intentionally...

Page 98: ...IL17569 Page 5 50 Effective June 2001 This page left blank intentionally...

Page 108: ...IL17569 Page 6 10 Effective June 2001 Figure 6 10 Common Ct Wiring Configurations...

Page 141: ...IL17569 Page 11 4 Effective June 2001 This page left blank intentionally...

Page 165: ...IL17569 Page Appendix 6 Effective June 2001 Figure 13 2 ANSI Very Inverse...

Page 166: ...Page Appendix 7 IL17569 Effective June 2001 Figure 13 3 ANSI Extremely Inverse...

Page 167: ...IL17569 Page Appendix 8 Effective June 2001 Figure 13 4 IEC A Figure 13 4 IEC A...

Page 168: ...Page Appendix 9 IL17569 Effective June 2001 Figure 13 5 IEC B...

Page 169: ...IL17569 Page Appendix 10 Effective June 2001 Figure 13 6 IEC C...

Page 170: ...Page Appendix 11 IL17569 Effective June 2001 Figure 13 7 IEC...

Page 171: ...IL17569 Page Appendix 12 Effective June 2001 Figure 13 8 ANSI...

Page 172: ...Page Appendix 13 IL17569 Effective June 2001 Figure 13 9 Thermal...

Page 173: ...IL17569 Page Appendix 14 Effective June 2001 Figure 13 10 Phase I4 t...

Page 174: ...Page Appendix 15 IL17569 Effective June 2001 Figure 13 11 Phase I2 t...

Page 175: ...IL17569 Page Appendix 16 Effective June 2001 Figure 13 12 Phase It...

Page 176: ...Page Appendix 17 IL17569 Effective June 2001 Figure 13 13 Phase 12 I4 t...

Page 177: ...IL17569 Page Appendix 18 Effective June 2001 Figure 13 14 Phase I2 t...

Page 178: ...Page Appendix 19 IL17569 Effective June 2001 Figure 13 15 Ground IT...

Page 180: ...Page Appendix 21 IL17569 Effective June 2001 This page left blank intentionally...

Page 187: ...Publication No IL17569 June 2001 Pittsburgh Pennsylvania U S A...