9 Appendix

9.1 Data image of the technology modules

XI/ON: XNE-GWBR-2ETH-MB

10/2011 MN05002008Z-EN

www.eaton.com

175

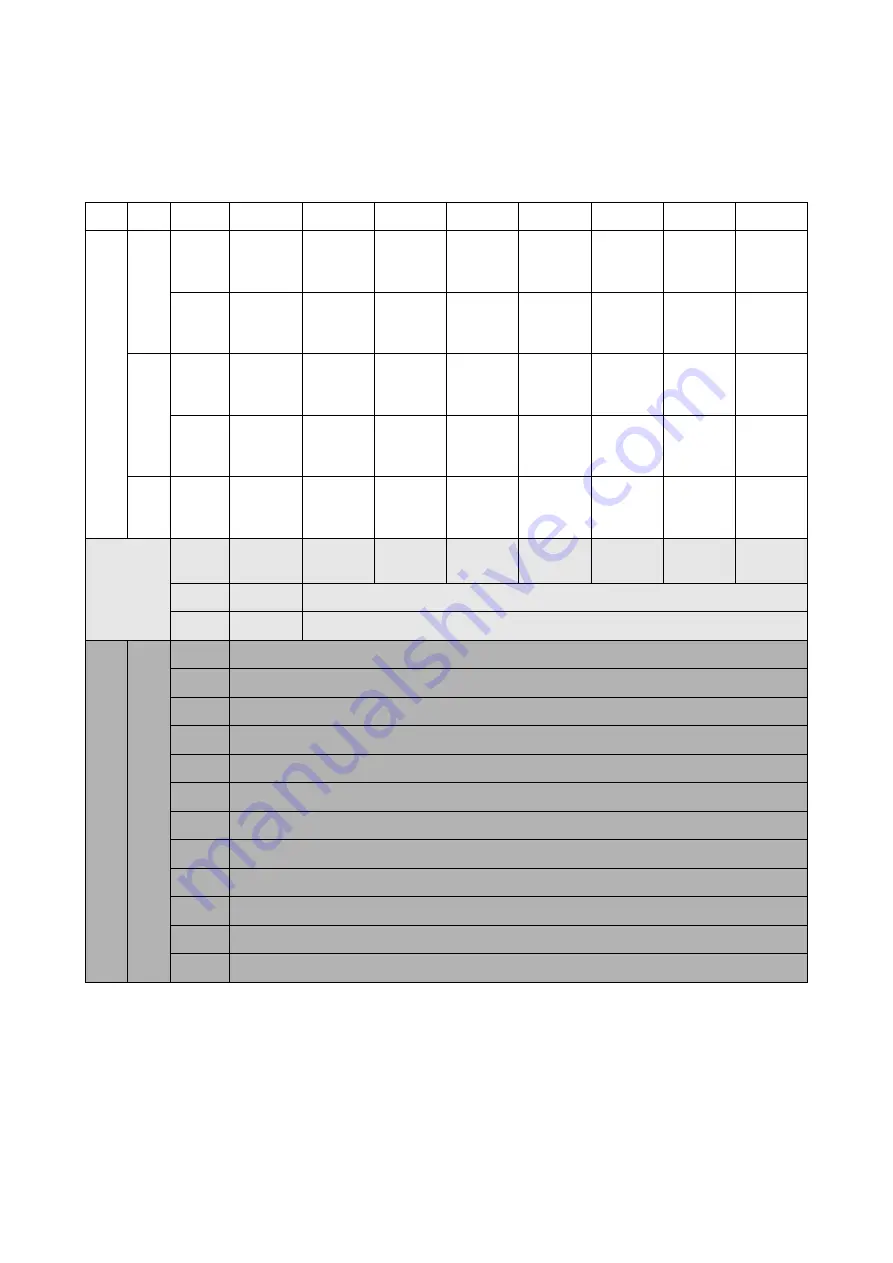

Process output data / control interface

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Control bytes

CNT x

0

reserved

CNT1_

SINGLE

CNT1_

SW_LR

CNT1_SFKT

_DISABLE

reserved

CNT1_

LOGMSG

CNT1_

ENABLE

CNT1_

GENERAL_

DISABLE

1

reserved

CNT2_

SINGLE

CNT2_

SW_LR

CNT2_SFKT

_DISABLE

reserved

CNT2_

LOGMSG

CNT2_

ENABLE

CNT2_

GENERAL_

DISABLE

PWM x

2

reserved

PWM1_

SINGLE

PWM1_

SW_LR

PWM1_

SFKT_

DISABLE

reserved

PWM1_

LOGMSG

PWM1_

ENABLE

PWM1_

GENERAL_

DISABLE

3

reserved

PWM2_

SINGLE

PWM2_

SW_LR

PWM2_

SFKT_

DISABLE

reserved

PWM2_

LOGMSG

PWM2_

ENABLE

PWM2_

GENERAL_

DISABLE

DOs

4

reserved

reserved

SET_P2

SET_ D2

reserved

reserved

SET_P1

SET_ D1

Regi

ster access

5

REG_WR

reserved

reserved

reserved

reserved

AUX_REG3_

WR_EN

AUX_REG2_

WR_EN

AUX_REG1_

WR_EN

6

reserved

REG_WR_ADR

7

reserved

REG_RD_ADR

Us

er

da

ta

8

REG_WR_DATA, byte 0

...

...

11

REG_WR_DATA, byte 3

12

AUX_REG1_WR_DATA, byte 0

...

...

15

AUX_REG1_WR_DATA, byte 3

16

AUX_REG2_WR_DATA, byte 0

...

...

19

AUX_REG2_WR_DATA, byte 3

20

AUX_REG3_WR_DATA, byte 0

...

...

23

AUX_REG3_WR_DATA, byte 3