EM78P911A

8-bit Micro-controller

__________________________________________________________________________________________________________________________________________________________________

* This specification is subject to change without notice.

~ ~

20

12/19/2005 (V2.1)

:

MOV 0X03,A

:

SWAPA A_BUFFER

;Return ACC

: RETI

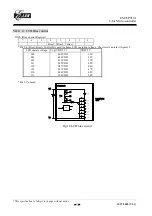

VII.7 Instruction Set

Instruction set has the following features:

(1). Every bit of any register can be set, cleared, or tested directly.

(2). The I/O register can be regarded as general register. That is, the same instruction can operates on I/O register.

The symbol "R" represents a register designator which specifies which one of the 64 registers (including

operational registers and general purpose registers) is to be utilized by the instruction. Bits 6 and 7 in R4 determine the

selected register bank. "b'' represents a bit field designator which selects the number of the bit, located in the register "R'',

affected by the operation. "k'' represents an 8 or 10-bit constant or literal value.

INSTRUCTION BINARY

HEX

MNEMONIC

OPERATION

STATUS

AFFECTE

D

0 0000 0000 0000

0000

NOP

No Operation

None

0 0000 0000 0001

0001

DAA

Decimal Adjust A

C

0 0000 0000 0010

0002

CONTW

A

→

CONT

None

0 0000 0000 0011

0003

SLEP

0

→

WDT, Stop oscillator

T,P

0 0000 0000 0100

0004

WDTC

0

→

WDT

T,P

0 0000 0000 rrrr

000r

IOW R

A

→

IOCR

None

0 0000 0001 0000

0010

ENI

Enable Interrupt

None

0 0000 0001 0001

0011

DISI

Disable Interrupt

None

0 0000 0001 0010

0012

RET

[Top of Stack]

→

PC

None

0 0000 0001 0011

0013

RETI

[Top of Stack]

→

PC

Enable Interrupt

None

0 0000 0001 0100

0014

CONTR

CONT

→

A

None

0 0000 0001 rrrr

001r

IOR R

IOCR

→

A

None

0 0000 0010 0000

0020

TBL

R2+A

→

R2 bits 9,10 do not

clear

Z,C,DC

0 0000 01rr rrrr

00rr

MOV R,A

A

→

R

None

0 0000 1000 0000

0080

CLRA

0

→

A

Z

0 0000 11rr rrrr

00rr

CLR R

0

→

R

Z

0 0001 00rr rrrr

01rr

SUB A,R

R-A

→

A

Z,C,DC

0 0001 01rr rrrr

01rr

SUB R,A

R-A

→

R

Z,C,DC

0 0001 10rr rrrr

01rr

DECA R

R-1

→

A

Z

0 0001 11rr rrrr

01rr

DEC R

R-1

→

R

Z

0 0010 00rr rrrr

02rr

OR A,R

A

∨

V

R

→

A

Z

0 0010 01rr rrrr

02rr

OR R,A

A

∨

V

R

→

R

Z

0 0010 10rr rrrr

02rr

AND A,R

A & R

→

A

Z

0 0010 11rr rrrr

02rr

AND R,A

A & R

→

R

Z

0 0011 00rr rrrr

03rr

XOR A,R

A

⊕

R

→

A

Z

0 0011 01rr rrrr

03rr

XOR R,A

A

⊕

R

→

R

Z

0 0011 10rr rrrr

03rr

ADD A,R

A + R

→

A

Z,C,DC

0 0011 11rr rrrr

03rr

ADD R,A

A + R

→

R

Z,C,DC

0 0100 00rr rrrr

04rr

MOV A,R

R

→

A

Z

0 0100 01rr rrrr

04rr

MOV R,R

R

→

R

Z

0 0100 10rr rrrr

04rr

COMA R

/R

→

A

Z

0 0100 11rr rrrr

04rr

COM R

/R

→

R

Z

0 0101 00rr rrrr

05rr

INCA R

R+1

→

A

Z