eSE Series

Pad Diagrams (V1.1) 01.17.2005

•

11

(These diagrams are subject to change without further notice)

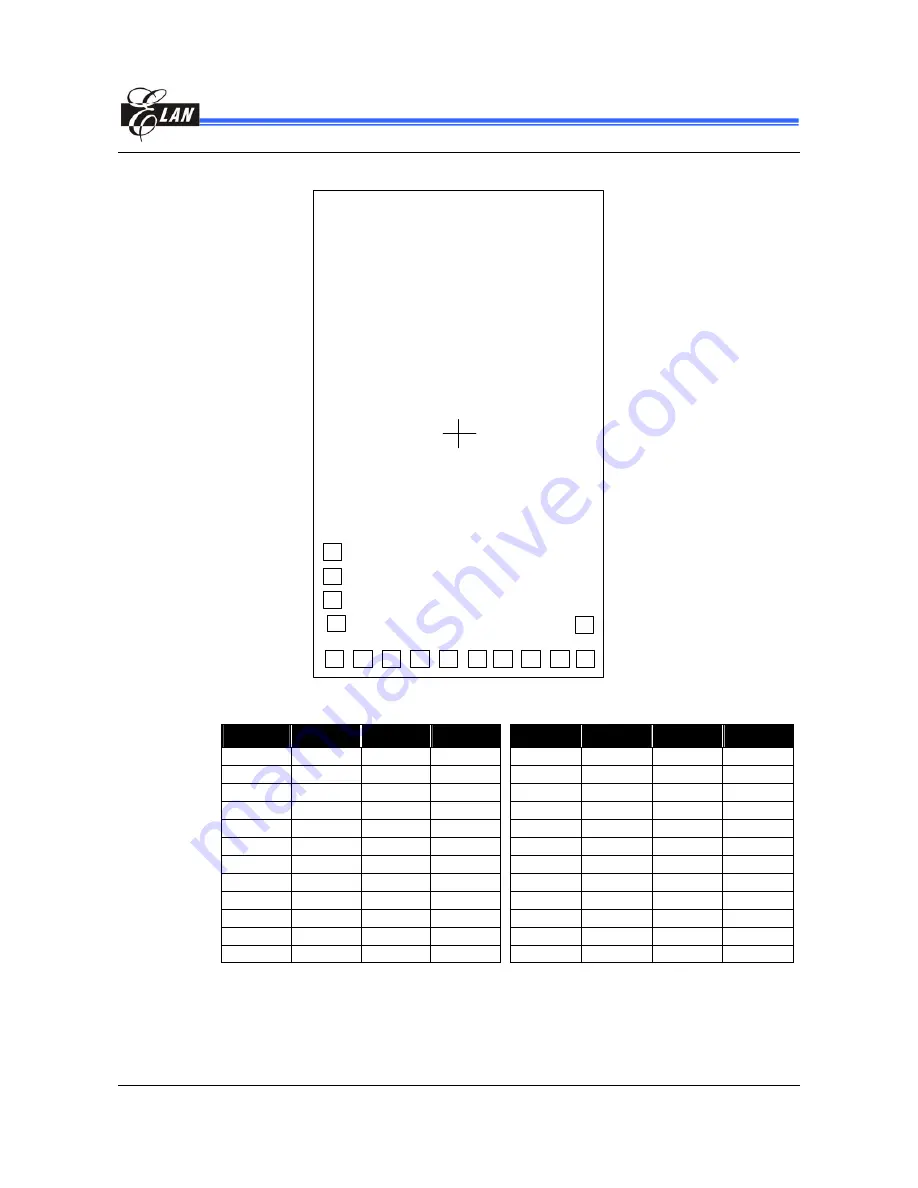

11 eSe080 Pad Diagram

VO2

VSSC

VO1

(0,0)

eSE080

4

5

6

7

8

9

10

11

12

13

14

P2

.2

P2

.3

P3

.0

P3

.1

P3

.2

P3

.3

VD

D

VCC

18

OSCI

15

16

17

VSSD

P2

.0

P2

.1

Pin No.

Symbol

X

Y

Pin No.

Symbol

X

Y

1 NC

13 P2.3

66.2

-1373.4

2 NC

14 P2.2

192.6

-1373.4

3 NC

15 P2.1

315.6

-1373.4

4 VCC

-588.0

-818.9 16 P2.0

442.0

-1373.4

5 VO2

-588.0

-938.9 17

VSSD

579.6

-1373.4

6 VSSC

-588.0

-1058.9 18 OSCI

573.4

-1196.5

7 VO1

-568.0

-1178.9 19 NC

8 VDD

-570.2

-1373.4 20 NC

9 P3.3

-432.6

-1373.4 21 NC

10 P3.2

-306.2

-1373.4 22 NC

11 P3.1

-183.2

-1373.4 23 NC

12 P3.0

-56.8

-1373.4 24 NC

Chip size : 1500 * 3100

µ

m

For PCB layout, IC substrate must be connected to VSS (negative power).

NOTE:

1. VO should be floating or connected to VSS (negative power) when not in use.

2. VSSD & VSSC should be connected together with negative power.

3. VCC & VDD should be of the same level with the positive power voltage.