ISL55180 EVM Getting Started

Rev A04: 11/28/2012

Copyright

Elevate Semiconductor Corporation 2012

Page 12 of 20

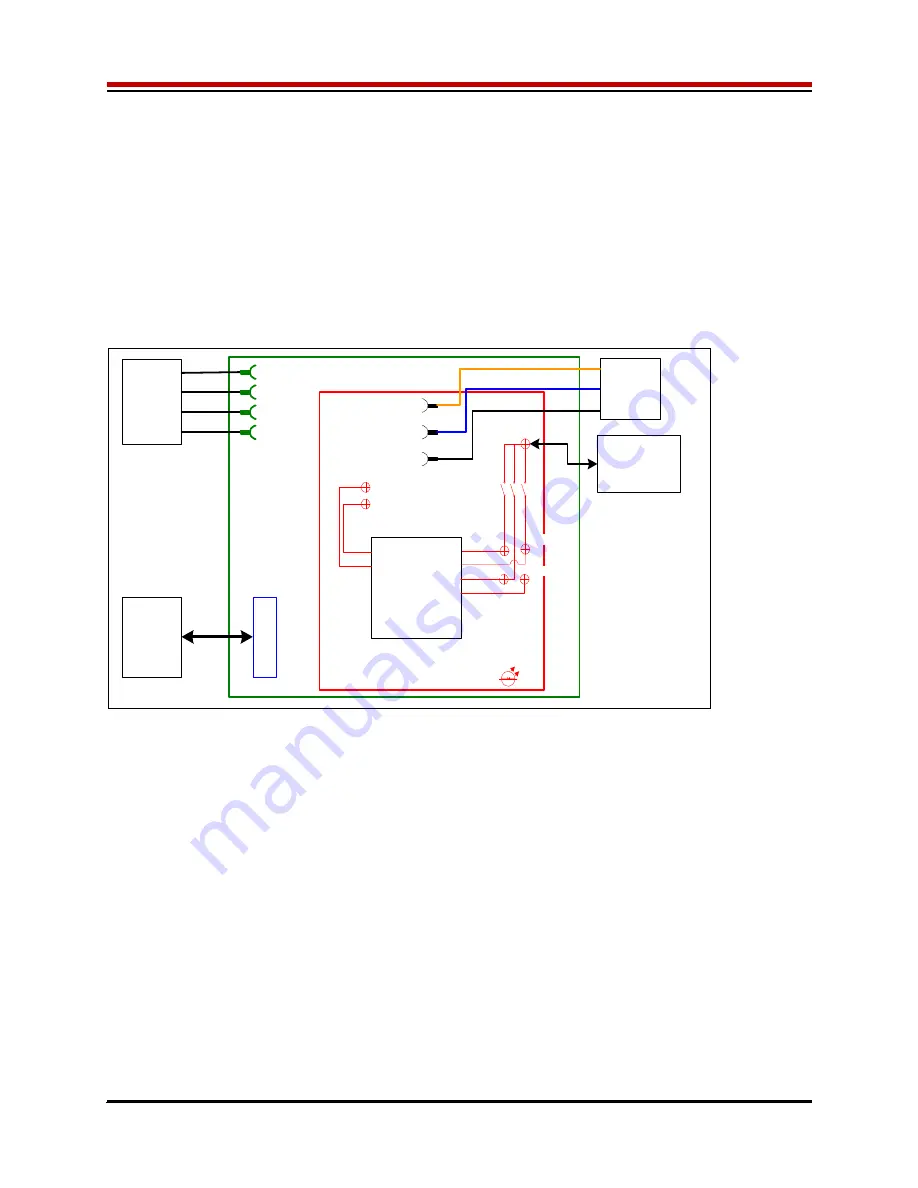

2.3.3 Channel#0 and Channel#1 Ganging (Merging) Configuration

Figure 4 illustrates the recommended configuration for the ganging application. Channel#0 is configured

in FV mode in Remote Sense while Channel#1 is configured in FI (Slave) mode. Both Channel#0 and

Channel#1 FORCE pins are connected to the TEST_NODE SMA. Channel#0 SENSE is also connected

to TEST_NODE which provides the remote Kelvin Sense return path.

The MI_MONITOR is configured to output the Channel#0 MI-S. The MONITOR is configured to output

the Channel#1 MI-S.

Channels 2-7 are configured in FV/MI mode.

Figure 4: ISL55180 EVM Ganging Configuration Simplified Block Diagram

Motherboard

Europa

Load Board

PC

J2

(FVMI

)

Parallel

Cable

EVM

Power

Supply

ISL55180

DMM

or

SMU

MONITOR (Ch1)

MONITOR

FORCE_0

SENSE_0

FORCE_0

VCCO

VEE

+20V (BN1)

-15V (BN2)

+5V (BN3)

GND (BN4)

LEDs

SENSE_0

TEST_NODE

Europa

Power

Supply

MI_MONITOR (Ch0)

MI_MONITOR

FORCE_1

SENSE_1

FORCE_1

SENSE_1

GND