CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72D

)

286

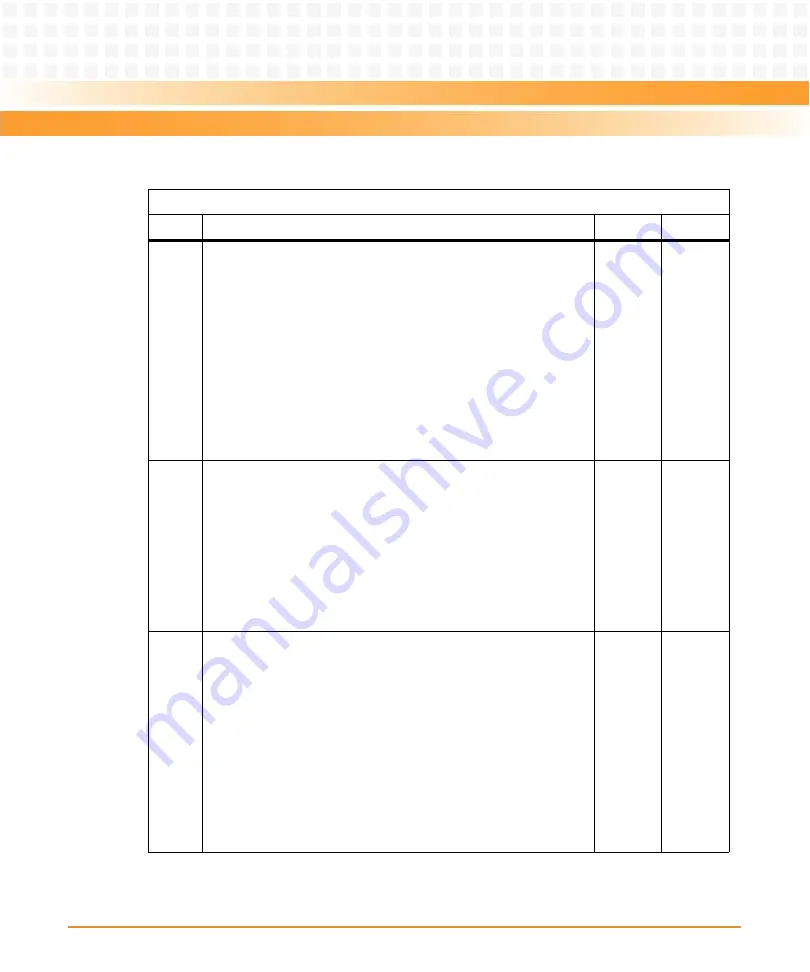

1

Overrun error (OE) indicator

When OE is set, it indicates that before the character in the RBR

was read, it was overwritten by the next character transferred into

the register. OE is cleared every time the CPU reads the contents of

the LSR. If the FIFO mode data continues to fill the FIFO beyond the

trigger level, an overrun error occurs only after the FIFO is full and

the next character has been completely received in the shift

register. An overrun error is indicated to the CPU as soon as it

happens. The character in the shift register is overwritten but it is

not transferred to the FIFO:

1: Overrun error occurred

0: No overrun error

0

GPP: r

2

Parity Error (PE) indicator

When PE is set, it indicates that the parity of the received data

character does not match the parity selected in the LCR (bit 4). PE

is cleared every time the CPU reads the contents of the LSR. In the

FIFO mode, this error is associated with the particular character in

the FIFO to which it applies. This error is revealed to the CPU when

its associated character is at the top of the FIFO:

1: Parity error occurred

0: No parity error

0

GPP: r

3

Framing Error (FE) indicator

When FE is set, it indicates that the received character did not have

a valid (set) stop bit. FE is cleared every time the CPU reads the

contents of the LSR. In the FIFO mode, this error is associated with

the particular character in the FIFO to which it applies. This error is

revealed to the CPU when its associated character is at the top of

the FIFO. The ACE tries to resynchronize after a framing error. To

accomplish this, it is assumed that the framing error is due to the

next start bit. The ACE samples this start bit twice and then

accepts the input data:

1: Framing error occurred

0: No framing error

0

GPP: r

Table 8-59 Line Status Register (LSR) (continued)

IO Address: Base + 5

Bit Description

Default

Access

Summary of Contents for ATCA-8310

Page 12: ...ATCA 8310 Installation and Use 6806800M72D Contents 12 Contents Contents ...

Page 26: ...ATCA 8310 Installation and Use 6806800M72D 26 List of Figures ...

Page 34: ...ATCA 8310 Installation and Use 6806800M72D About this Manual 34 About this Manual ...

Page 54: ...Hardware Preparation and Installation ATCA 8310 Installation and Use 6806800M72D 54 ...

Page 70: ...Controls Indicators and Connectors ATCA 8310 Installation and Use 6806800M72D 70 ...

Page 162: ...BIOS ATCA 8310 Installation and Use 6806800M72D 162 ...

Page 200: ...U Boot ATCA 8310 Installation and Use 6806800M72D 200 ...

Page 244: ...Intelligent Peripheral Management Controller ATCA 8310 Installation and Use 6806800M72D 244 ...

Page 438: ...CPLD and FPGA ATCA 8310 Installation and Use 6806800M72D 438 ...

Page 442: ...Replacing the Battery ATCA 8310 Installation and Use 6806800M72D 442 ...

Page 444: ...Related Documentation ATCA 8310 Installation and Use 6806800M72D 444 ...

Page 454: ...ATCA 8310 Installation and Use 6806800M72D Sicherheitshinweise 454 ...

Page 456: ...Index ATCA 8310 Installation and Use 6806800M72D 456 ...

Page 457: ...Index ATCA 8310 Installation and Use 6806800M72D 457 ...

Page 458: ...Index ATCA 8310 Installation and Use 6806800M72D 458 ...

Page 459: ......