Memory Maps and Addresses

CPCI-6200 Installation and Use (6806800J66C

)

158

7.4.14 NAND Flash Chip 2 Select Register

ALE

Address Latch Enable

1

ALE is asserted when the device is accessed.

0

ALE is not asserted when the device is accessed.

WP

Write Protect

1

WP is asserted when the device is accessed.

0

WP is not asserted when the device is accessed.

RSVD

Reserved

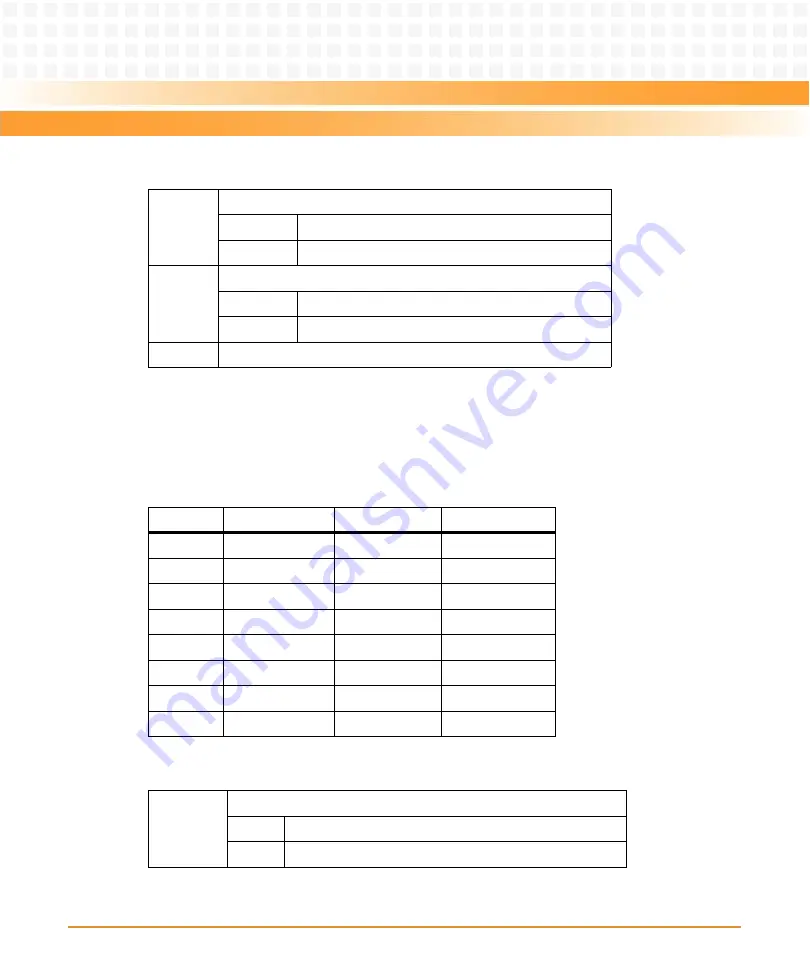

Table 7-30 NAND Flash Chip 2 Control Register Field Definition

Table 7-31 NAND Flash Chip 2 Select Register, 0xF200_0015

Bit

Field

Operation

Reset

7

CE1

R/W

0

6

CE2

R/W

0

5

CE3

R/W

0

4

CE4

R/W

0

3

RSVD

R

0

2

RSVD

R

0

1

RSVD

R

0

0

RSVD

R

0

Table 7-32 NAND Flash Chip 2 Select Register

CE1

Chip Enable 1

1

CE1 is asserted when the device is accessed.

0

CE1 is not asserted when the device is accessed.

Summary of Contents for CPCI-6200

Page 14: ...CPCI 6200 Installation and Use 6806800J66C 14 List of Figures ...

Page 20: ...CPCI 6200 Installation and Use 6806800J66C About this Manual 20 About this Manual ...

Page 28: ...Introduction CPCI 6200 Installation and Use 6806800J66C 28 ...

Page 44: ...Hardware Preparation and Installation CPCI 6200 Installation and Use 6806800J66C 44 ...

Page 70: ...Controls LEDs and Connectors CPCI 6200 Installation and Use 6806800J66C 70 ...

Page 106: ...MOTLoad Firmware CPCI 6200 Installation and Use 6806800J66C 106 ...

Page 178: ...Memory Maps and Addresses CPCI 6200 Installation and Use 6806800J66C 178 ...

Page 195: ......