RXi2-UP IPC Hardware Reference Manual

Section 7

GFK-3047D

Oct 2021

Hardware and Firmware Programmable Devices

48

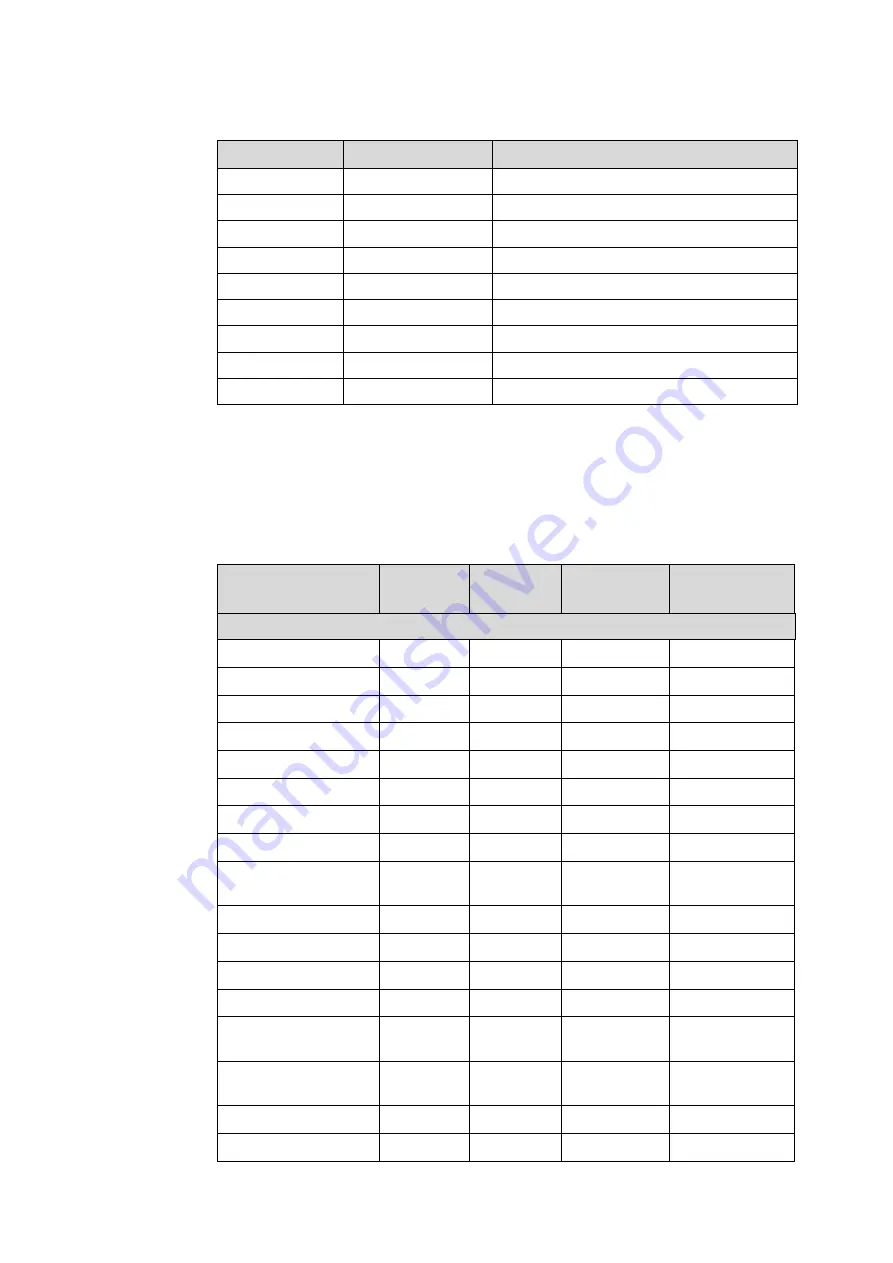

Table 7-3

PCI Express Port Usage

Source Device

Port

Connected to

COMe PEG

0:3

Riser board

COMe PEG

8:11

M.2 mass storage device

COMe PCIe

0

Ethernet #1

COMe PCIe

1

Ethernet #2

COMe PCIe

2

Ethernet #3

COMe PCIe

3

Ethernet #4

COMe PCIe

4

M.2 A-Key

COMe PCIe

5

UART

COMe PCIe

6

mPCIe

7.4

PCI Routing

The PCI routings in an RXi2-UP IPC are defined in the following table.

Table 7-4

PCI Routing

Function

Connected

to

Vendor

Device (GPU

Dependent)

Bus/Dev/Func

bCOM6L20

Intel Skylake Host Bridge

—

8086

—

0/00/0

HD Graphics

—

8086

—

0/2/0

Gaussian mixture model

—

8086

—

0/8/0

Intel USB 3.0 XHCI

—

8086

—

0/14/0

Intel Thermal Subsystem

—

8086

—

0/14/2

Serial I/O I2C #0

—

8086

—

0/15/0

Serial I/O I2C #1

—

8086

—

0/152

Intel CSME HECI

—

8086

—

0/16/0

Intel SATA Controller

[AHCI]

—

8086

—

0/17/0

PCI Bridge

I210 #1

8086

—

0/1C/0

PCI Bridge

I210 #2

8086

—

0/1C/1

PCI Bridge

I210 #3

8086

—

0/1C/2

PCI Bridge

I210 #4

8086

—

0/1C/3

PCI Bridge

M.2 A-Key

Slot

8086

—

0/1C/4

PCI Bridge

Pericom

UART

8086

—

0/1C/5

PCI Bridge

mPCIe Slot

8086

—

0/1C/6

Intel LPC Controller

8086

—

0/1F/0