Endace Measurement Systems Limited

http://www.endace.com

EDM01.05-12r1 DAG 3.7T Card User Manual

Copyright, all rights reserved.

2

Version 6. 22 September 2005.

1.2 DAG 3.7T Card Product Description

Description

The DAG 3.7T cards are PCI bus cards designed for cell and packet

capture and generation on telecommunication networks. The card's key

features include:

•

16 T1 or E1 Network Interfaces

•

A Spartan III FPGA supporting high-performance Endace Firmware

•

An Intel XScale IO Processor

•

Support for receiving and sending Channelised, Unchannelised, and

Fractional T1/E1, HDLC and non-HDLC data traffic.

•

Support for data traffic filtering.

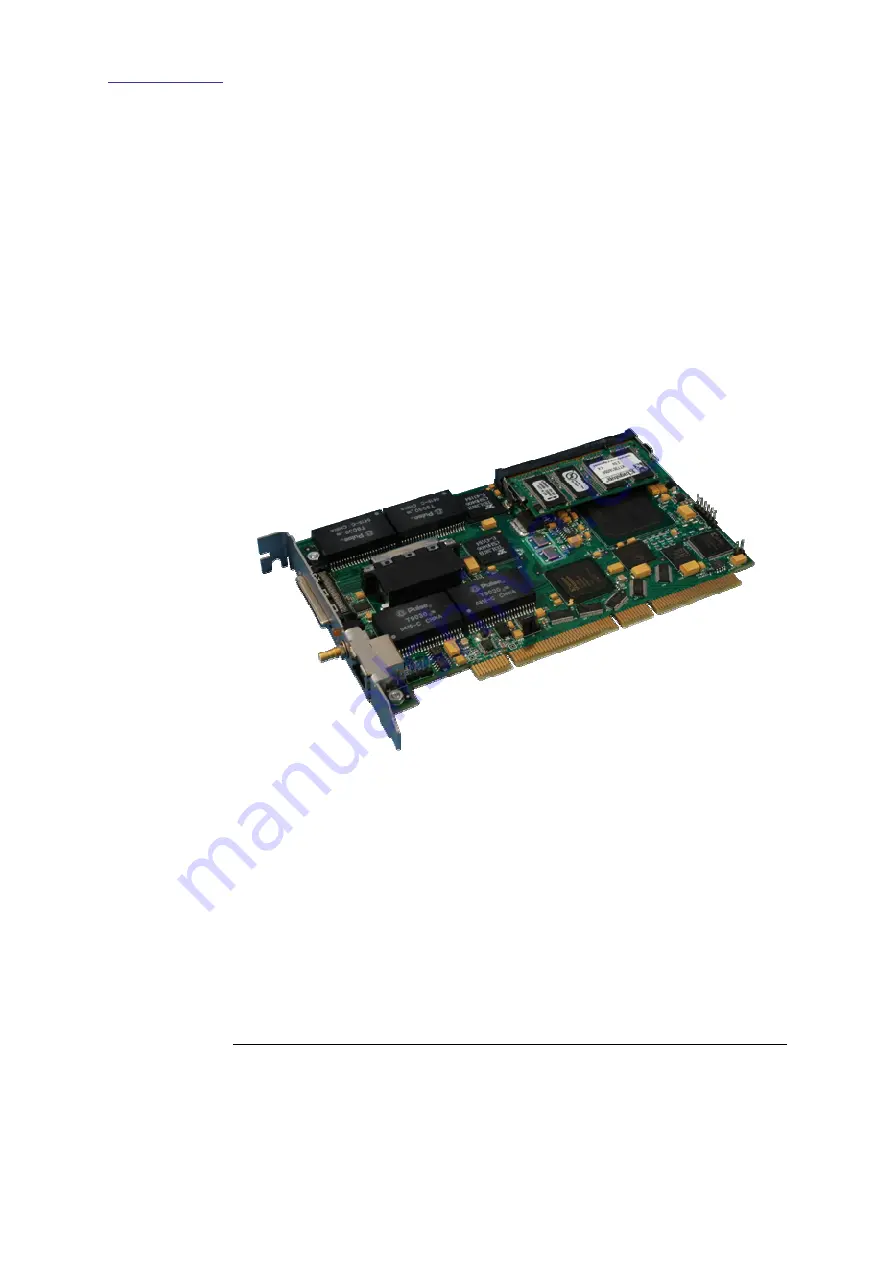

Figure

Figure 1-1 shows the DAG 3.7T Card.

Figure 1-1. DAG 3.7T Card.

1.3 DAG 3.7T Architecture

Description

The TDM T1 or E1 data is received by the 16 RJ45 interfaces, and passed

through line interface units. The data is then fed immediately into the

FPGA for deframing and demapping into HDLC frames.

This FPGA contains an Ethernet processor and the DUCK timestamp

engine. Because of component close association, packets or cells are

time-stamped accurately. Time stamped packet records are then stored in

the lower FIFO.

Continued on next page