14

EPSON

E0C6006 TECHNICAL MANUAL

CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (Oscillation Circuit)

4.3.6 I/O memory of oscillation circuit

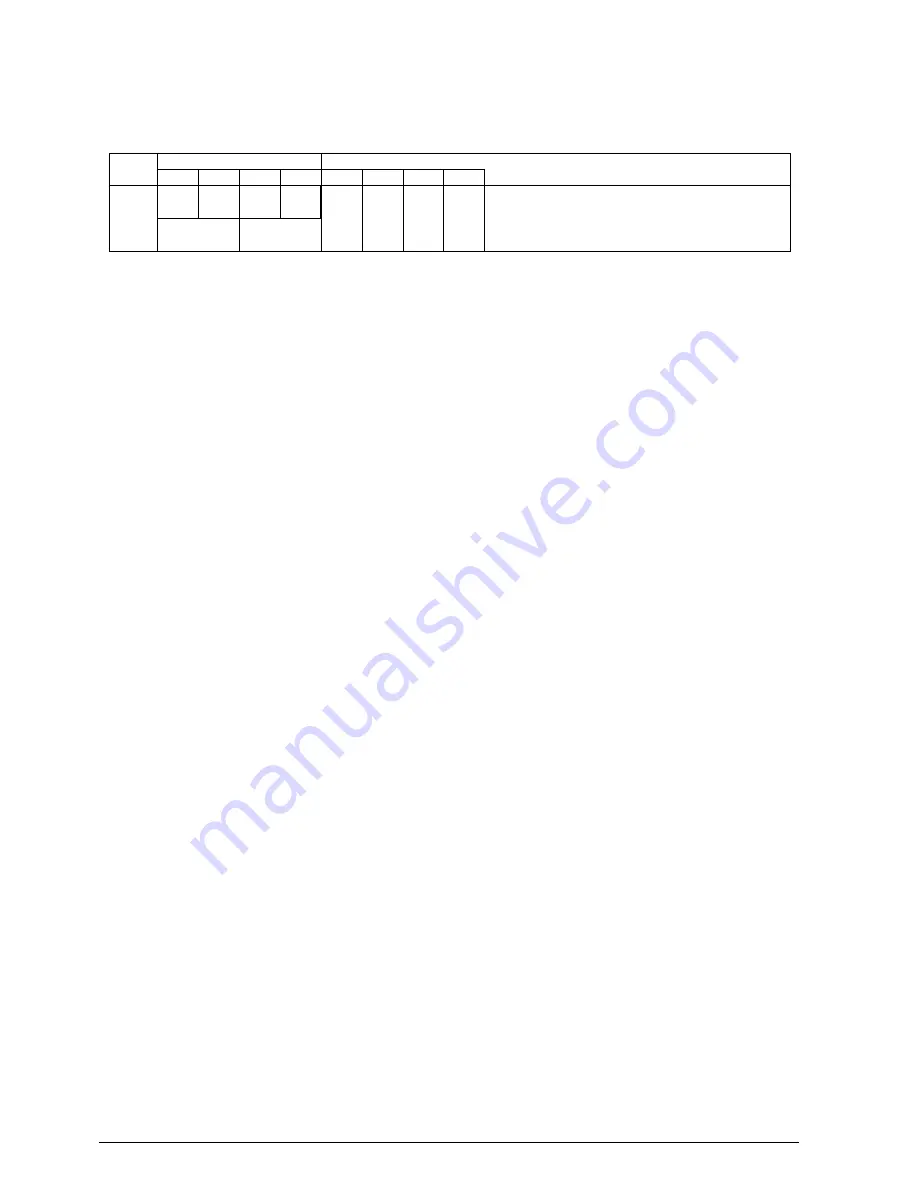

Table 4.3.6.1 shows the I/O address and the control bits for the oscillation circuit.

Table 4.3.6.1 Control bits of oscillation circuit

Address

Comment

D3

D2

Register

D1

D0

Name

Init

∗

1

1

0

0F6H

0

0

CLKCHG OSCC

R

R/W

0

∗

3

0

∗

3

CLKCHG

OSCC

–

∗

2

–

∗

2

0

1

–

–

OSC1

On

–

–

OSC3

Off

Unused

Unused

CPU clock change

OSC3 oscillation on/off

∗

1

∗

2

Initial value at initial reset

Not set in the circuit

∗

5 Undefined

∗

3

∗

4

Always "0" being read

Reset (0) immediately after being read

OSCC: OSC3 oscillation control register (0F6H•D0)

Controls oscillation for the OSC3 oscillation circuit.

When "1" is written: OSC3 oscillation ON

When "0" is written: OSC3 oscillation OFF

Reading: Valid

When it is necessary to operate the CPU at high speed or output a remote control carrier signal, set OSCC

to "1". At other times, set it to "0" to reduce current consumption.

At initial reset, this register is set to "1".

CLKCHG: CPU system clock switching register (0F6H•D1)

The CPU's operation clock is selected with this register.

When "1" is written: OSC1 clock is selected

When "0" is written: OSC3 clock is selected

Reading: Valid

When the CPU clock is to be OSC3, set CLKCHG to "0"; for OSC1, set CLKCHG to "1".

After turning the OSC3 oscillation ON (OSCC = "1"), switching of the clock should be done after waiting

5 msec or more.

At initial reset, this register is set to "0".

4.3.7 Programming notes

(1) It takes at least 5 msec from the time the OSC3 oscillation circuit goes on until the oscillation stabi-

lizes. Consequently, when switching the CPU operation clock from OSC1 to OSC3, do this after a

minimum of 5 msec have elapsed since the OSC3 oscillation went on.

Further, the oscillation stabilization time varies depending on the external oscillator characteristics

and conditions of use, so allow ample margin when setting the wait time.

(2) When switching the clock from OSC3 to OSC1, use a separate instruction for switching the OSC3

oscillation off. An error in the CPU operation can result if this processing is performed at the same

time by the one instruction.