E0C6006 TECHNICAL MANUAL

EPSON

45

CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (Interrupt and HALT)

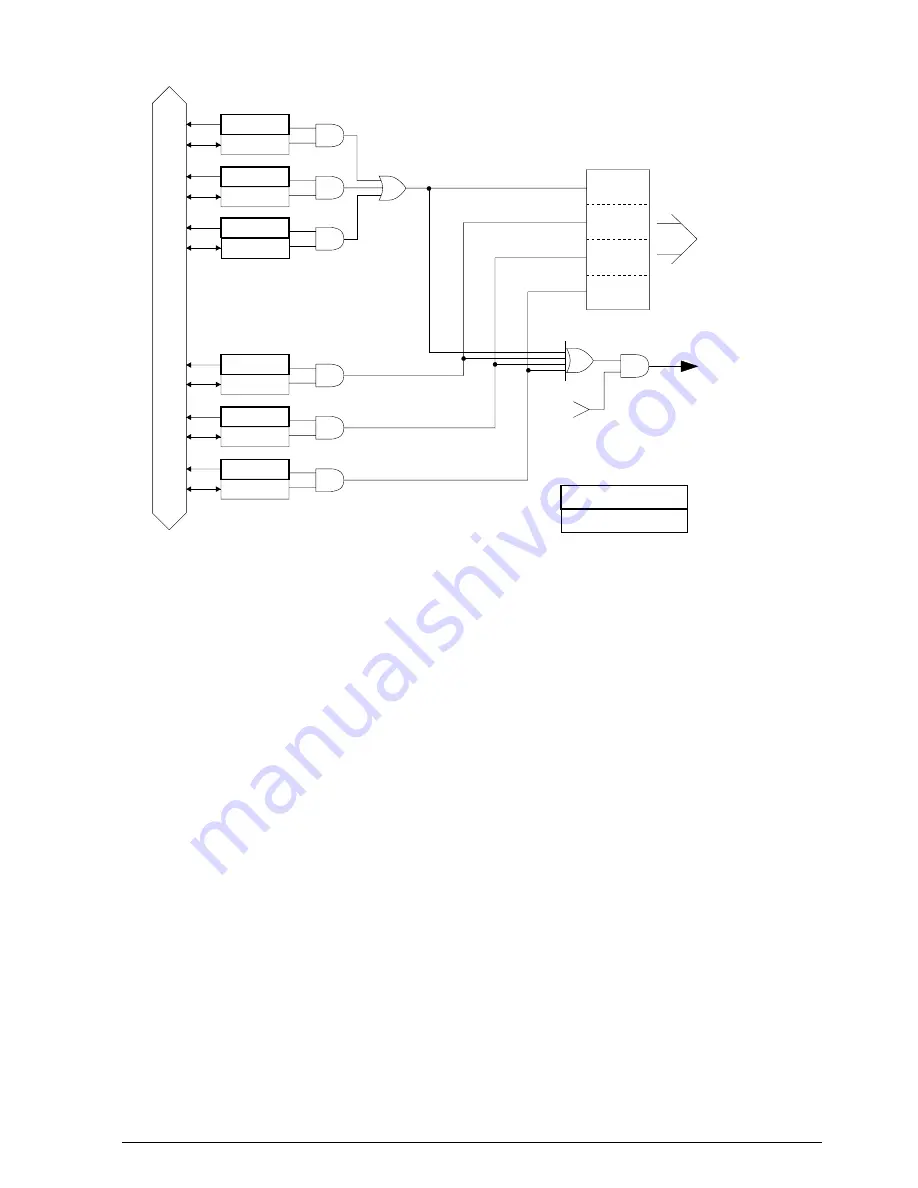

TI2

ETI2

TI8

ETI8

IREM

EIREM

IK1

EIK1

IK0

EIK0

Data bus

IF

INT

(interrupt request)

(MSB)

(LSB)

Interrupt vector

Program

counter

TI32

ETI32

Interrupt factor flag

Interrupt mask register

Fig. 4.10.3.1 Interrupt request/interrupt vector generation circuit

4.10.4 Programming notes

(1) Restart from the HALT mode is performed by an interrupt. The return address after completion of the

interrupt processing will be the address following the HALT instruction.

(2) When an interrupt occurs, the interrupt flag will be reset by the hardware and it will become DI

status. After completion of the interrupt processing, set to the EI status through the software as

needed.

Moreover, the nesting level may be set to be programmable by setting to the EI state at the beginning

of the interrupt processing routine.

(3) The interrupt factor flags must always be reset before setting the EI status. When the interrupt mask

register has been set to "1", the same interrupt will occur again if the EI status is set unless of resetting

the interrupt factor flag.

(4) The interrupt factor flag will be reset by reading through the software. Because of this, when multiple

interrupt factor flags are to be assigned to the same address, perform the flag check after the contents

of the address has been stored in the RAM. Direct checking with the FAN instruction will cause all the

interrupt factor flag to be reset.

(5) Reading of interrupt factor flag is available at EI, but be careful in the following cases.

If the interrupt mask register value corresponding to the interrupt factor flag to be read is set to "1", an

interrupt request will be generated by the interrupt factor flag set timing, or an interrupt request will

not be generated. Be very careful when interrupt factor flags are in the same address.