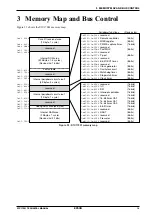

3 MEMORY MAP AND BUS CONTROL

18

EPSON

S1C17001 TECHNICAL MANUAL

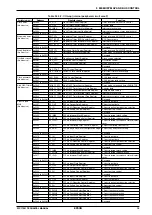

3.4.3 I/O

Map

The I/O map for the internal peripheral circuit area is shown below. For more information on control registers, refer

to the I/O register list in the Appendix or the corresponding peripheral circuit explanations.

Note: Addresses indicated as “Reserved” or blank unused peripheral circuit areas should not be ac-

cessed by application programs.

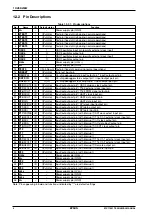

Table 3.4.3.1: I/O map (internal peripheral circuit area 1)

Peripheral circuit

Address

Register name

Function

Prescaler

(8-bit device)

0x4020

PSC_CTL

Prescaler Control Register

Prescaler start/stop control

0x4021 to 0x403f –

–

Reserved

UART (with IrDA)

(8-bit device)

0x4100

UART_ST

UART Status Register

Transfer, buffer, and error status display

0x4101

UART_TXD

UART Transmit Data Register

Transmission data

0x4102

UART_RXD

UART Receive Data Register

Received data

0x4103

UART_MOD

UART Mode Register

Transfer data format setting

0x4104

UART_CTL

UART Control Register

Data transfer control

0x4105

UART_EXP

UART Expansion Register

IrDA mode setting

0x4106 to 0x411f –

–

Reserved

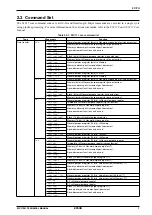

8-bit timer

(with F mode)

(16-bit device)

0x4200

T8F_CLK

8-bit Timer Input Clock Select Register

Prescaler output clock selection

0x4202

T8F_TR

8-bit Timer Reload Data Register

Reload data setting

0x4204

T8F_TC

8-bit Timer Counter Data Register

Counter data

0x4206

T8F_CTL

8-bit Timer Control Register

Timer mode setting and timer RUN/STOP

0x4208 to 0x421f –

–

Reserved

16-bit timer Ch.0

(16-bit device)

0x4220

T16_CLK0

16-bit Timer Ch.0 Input Clock Select Register Prescaler output clock selection

0x4222

T16_TR0

16-bit Timer Ch.0 Reload Data Register

Reload data setting

0x4224

T16_TC0

16-bit Timer Ch.0 Counter Data Register

Counter data

0x4226

T16_CTL0

16-bit Timer Ch.0 Control Register

Timer mode setting and timer RUN/STOP

0x4228 to 0x423f –

–

Reserved

16-bit timer Ch.1

(16-bit device)

0x4240

T16_CLK1

16-bit Timer Ch.1 Input Clock Select Register Prescaler output clock selection

0x4242

T16_TR1

16-bit Timer Ch.1 Reload Data Register

Reload data setting

0x4244

T16_TC1

16-bit Timer Ch.1 Counter Data Register

Counter data

0x4246

T16_CTL1

16-bit Timer Ch.1 Control Register

Timer mode setting and timer RUN/STOP

0x4248 to 0x425f –

–

Reserved

16-bit timer Ch.2

(16-bit device)

0x4260

T16_CLK2

16-bit Timer Ch.2 Input Clock Select Register Prescaler output clock selection

0x4262

T16_TR2

16-bit Timer Ch.2 Reload Data Register

Reload data setting

0x4264

T16_TC2

16-bit Timer Ch.2 Counter Data Register

Counter data

0x4266

T16_CTL2

16-bit Timer Ch.2 Control Register

Timer mode setting and timer RUN/STOP

0x4268 to 0x427f –

–

Reserved

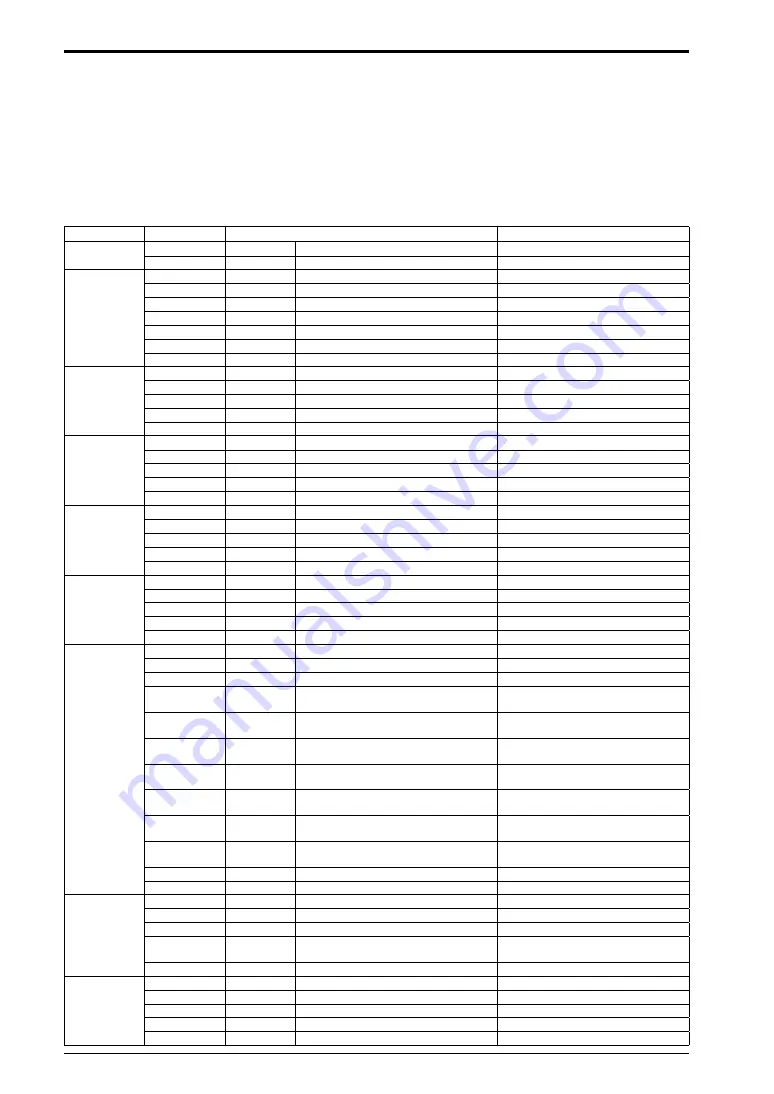

Interrupt

controller

(16-bit device)

0x4300

ITC_IFLG

Interrupt Flag Register

Interrupt occurrence status display/reset

0x4302

ITC_EN

Interrupt Enable Register

Maskable interrupt permission/prohibition

0x4304

ITC_CTL

ITC Control Register

ITC operation permission/prohibition

0x4306

ITC_ELV0

External Interrupt Level Setup Register 0

P0/P1 port interrupt level and trigger mode

setting

0x4308

ITC_ELV1

External Interrupt Level Setup Register 1

Stopwatch timer and clock timer interrupt

level and trigger mode setting

0x430a

ITC_ELV2

External Interrupt Level Setup Register 2

8-bit OSC1 timer interrupt level and trigger

mode setting

0x430c

ITC_ELV3

External Interrupt Level Setup Register 3

PWM & capture timer interrupt level and

trigger mode setting

0x430e

ITC_ILV0

Internal Interrupt Level Setup Register 0

8-bit timer and 16-bit timer Ch.0 interrupt

level setting

0x4310

ITC_ILV1

Internal Interrupt Level Setup Register 1

16-bit timer Ch.1 and 16-bit timer Ch.2

interrupt level setting

0x4312

ITC_ILV2

Internal Interrupt Level Setup Register 2

UART and remote controller interrupt level

setting

0x4314

ITC_ILV3

Internal Interrupt Level Setup Register 3

SPI and I

2

C interrupt level setting

0x4316 to 0x431f –

–

Reserved

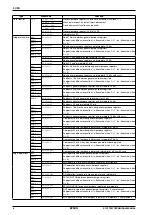

SPI

(16-bit device)

0x4320

SPI_ST

SPI Status Register

Transfer and buffer status display

0x4322

SPI_TXD

SPI Transmit Data Register

Transmission data

0x4324

SPI_RXD

SPI Receive Data Register

Received data

0x4326

SPI_CTL

SPI Control Register

SPI mode and data transfer permission

setting

0x4328 to 0x433f –

–

Reserved

I

2

C

(16-bit device)

0x4340

I2C_EN

I

2

C Enable Register

I

2

C module enable

0x4342

I2C_CTL

I

2

C Control Register

I

2

C control and transfer status display

0x4344

I2C_DAT

I

2

C Data Register

Transfer data

0x4346

I2C_ICTL

I

2

C Interrupt Control Register

I

2

C interrupt control

0x4348 to 0x435f –

–

Reserved

Summary of Contents for S1C17001

Page 1: ...Technical Manual S1C17001 CMOS 16 BIT SINGLE CHIP MICROCONTROLLER ...

Page 33: ...4 POWER SUPPLY VOLTAGE 24 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 63: ...6 INITERRUPT CONTROLLER 54 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 87: ...8 CLOCK GENERATOR CLG 78 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 91: ...9 PRESCALER PSC 82 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 133: ...11 16 BIT TIMER T16 124 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 211: ...16 STOPWATCH TIMER SWT 202 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 219: ...17 WATCHDOG TIMER WDT 210 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 241: ...18 UART 232 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 277: ...20 I2 C 268 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 313: ...25 PACKAGE 304 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...