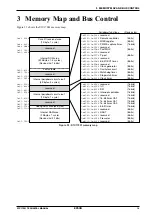

3 MEMORY MAP AND BUS CONTROL

S1C17001 TECHNICAL MANUAL

EPSON

19

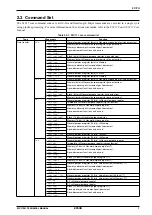

Table 3.4.3.2: I/O map (internal peripheral circuit area 2)

Peripheral circuit

Address

Register name

Function

Clock timer

(8-bit device)

0x5000

CT_CTL

Clock Timer Control Register

Timer reset and RUN/STOP control

0x5001

CT_CNT

Clock Timer Counter Register

Counter data

0x5002

CT_IMSK

Clock Timer Interrupt Mask Register

Interrupt mask setting

0x5003

CT_IFLG

Clock Timer Interrupt Flag Register

Interrupt occurrence status display/reset

0x5004 to 0x501f –

–

Reserved

Stopwatch timer

(8-bit device)

0x5020

SWT_CTL

Stopwatch Timer Control Register

Timer reset and RUN/STOP control

0x5021

SWT_BCNT

Stopwatch Timer BCD Counter Register

BCD Counter data

0x5022

SWT_IMSK

Stopwatch Timer Interrupt Mask Register

Interrupt mask setting

0x5023

SWT_IFLG

Stopwatch Timer Interrupt Flag Register

Interrupt occurrence status display/reset

0x5024 to 0x503f –

–

Reserved

Watchdog timer

(8-bit device)

0x5040

WDT_CTL

Watchdog Timer Control Register

Timer reset and RUN/STOP control

0x5041

WDT_ST

Watchdog Timer Status Register

Timer mode setting and NMI status display

0x5042 to 0x505f –

–

Reserved

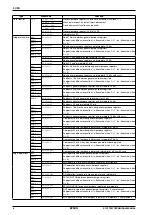

Oscillator circuit

(8-bit device)

0x5060

OSC_SRC

Clock Source Select Register

Clock source selection

0x5061

OSC_CTL

Oscillation Control Register

Oscillation control

0x5062

OSC_NFEN

Noise Filter Enable Register

Noise filter ON/OFF

0x5063

–

–

Reserved

0x5064

OSC_FOUT

FOUT Control Register

Clock external output control

0x5065

OSC_T8OSC1 T8OSC1 Clock Control Register

8-bit OSC1 timer clock setting

0x5066 to 0x507f –

–

Reserved

Clock generator

(8-bit device)

0x5080

CLG_PCLK

PCLK Control Register

PCLK feed control

0x5081

CLG_CCLK

CCLK Control Register

CCLK division ratio setting

0x5082 to 0x509f –

–

Reserved

8-bit OSC1 timer

(8-bit device)

0x50c0

T8OSC1_CTL

8-bit OSC1 Timer Control Register

Timer mode setting and timer RUN/STOP

0x50c1

T8OSC1_CNT

8-bit OSC1 Timer Counter Data Register

Counter data

0x50c2

T8OSC1_CMP 8-bit OSC1 Timer Compare Data Register

Compare data setting

0x50c3

T8OSC1_IMSK 8-bit OSC1 Timer Interrupt Mask Register

Interrupt mask setting

0x50c4

T8OSC1_IFLG 8-bit OSC1 Timer Interrupt Flag Register

Interrupt occurrence status display/reset

0x50c5 to 0x50df –

–

Reserved

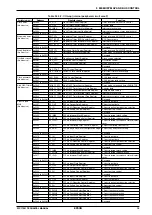

P port & port

MUX

(8-bit device)

0x5200

P0_IN

P0 Port Input Data Register

P0 port input data

0x5201

P0_OUT

P0 Port Output Data Register

P0 port output data

0x5202

P0_IO

P0 Port I/O Direction Control Register

P0 port input/output direction selection

0x5203

P0_PU

P0 Port Pull-up Control Register

P0 port pull-up control

0x5204

–

–

Reserved

0x5205

P0_IMSK

P0 Port Interrupt Mask Register

P0 port interrupt mask setting

0x5206

P0_EDGE

P0 Port Interrupt Edge Select Register

P0 port interrupt edge selection

0x5207

P0_IFLG

P0 Port Interrupt Flag Register

P0 port interrupt occurrence status display/

reset

0x5208

P0_CHAT

P0 Port Chattering Filter Control Register

P0 port chattering filter control

0x5209

P0_KRST

P0 Port Key-Entry Reset Configuration Regis-

ter

P0 port key entry reset setting

0x520a to 0x520f –

–

Reserved

0x5210

P1_IN

P1 Port Input Data Register

P1 port input data

0x5211

P1_OUT

P1 Port Output Data Register

P1 port output data

0x5212

P1_IO

P1 Port I/O Direction Control Register

P1 port input/output direction selection

0x5213

P1_PU

P1 Port Pull-up Control Register

P1 port pull-up control

0x5214

–

–

Reserved

0x5215

P1_IMSK

P1 Port Interrupt Mask Register

P1 port interrupt mask setting

0x5216

P1_EDGE

P1 Port Interrupt Edge Select Register

P1 port interrupt edge selection

0x5217

P1_IFLG

P1 Port Interrupt Flag Register

P1 port interrupt occurrence status display/

reset

0x5218 to 0x521f –

–

Reserved

0x5220

P2_IN

P2 Port Input Data Register

P2 port input data

0x5221

P2_OUT

P2 Port Output Data Register

P2 port output data

0x5222

P2_IO

P2 Port I/O Direction Control Register

P2 port input/output direction selection

0x5223

P2_PU

P2 Port Pull-up Control Register

P2 port pull-up control

0x5224 to 0x522f –

–

Reserved

0x5230

P3_IN

P3 Port Input Data Register

P3 port input data

0x5231

P3_OUT

P3 Port Output Data Register

P3 port output data

0x5232

P3_IO

P3 Port I/O Direction Control Register

P3 port input/output direction selection

0x5233

P3_PU

P3 Port Pull-up Control Register

P3 port pull-up control

0x5234 to 0x527f –

–

Reserved

0x52a0

P0_PMUX

P0 Port Function Select Register

P0 port function selection

0x52a1

P1_PMUX

P1 Port Function Select Register

P1 port function selection

0x52a2

P2_PMUX

P2 Port Function Select Register

P2 port function selection

0x52a3

P3_PMUX

P3 Port Function Select Register

P3 port function selection

0x52a4 to 0x52bf –

–

Reserved

Summary of Contents for S1C17001

Page 1: ...Technical Manual S1C17001 CMOS 16 BIT SINGLE CHIP MICROCONTROLLER ...

Page 33: ...4 POWER SUPPLY VOLTAGE 24 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 63: ...6 INITERRUPT CONTROLLER 54 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 87: ...8 CLOCK GENERATOR CLG 78 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 91: ...9 PRESCALER PSC 82 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 133: ...11 16 BIT TIMER T16 124 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 211: ...16 STOPWATCH TIMER SWT 202 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 219: ...17 WATCHDOG TIMER WDT 210 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 241: ...18 UART 232 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 277: ...20 I2 C 268 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 313: ...25 PACKAGE 304 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...