21 REMOTE CONTROLLER (REMC)

282

EPSON

S1C17001 TECHNICAL MANUAL

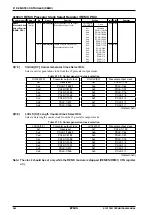

0x5343: REMC L Carrier Length Setup Register (REMC_CARL)

Register name Address

Bit

Name

Function

Setting

Init. R/W

Remarks

REMC L Carrier

Length Setup

Register

(REMC_CARL)

0x5343

(8 bits)

D7–6

–

reserved

–

–

–

0 when being read.

D5–0

REMCL[5:0]

L carrier length setup

0x0 to 0x3f

0x0

R/W

D[7:6] Reserved

D[5:0]

REMCL[5:0]: L Carrier Length Setup Bits

Set the carrier signal L section length. (Default: 0x0)

Specify a value corresponding to the number of carrier generation clock cycles selected by CG-

CLK[3:0] (D[7:4]/REMC_PSC register) + 1.

Calculate carrier L section length as follows:

REMCL + 1

Carrier L section length = —————— [s]

clk_in

REMCH: REMCL[5:0] settings

clk_in: Prescaler output clock frequency

The H section length is specified by REMCH[5:0] (D[5:0]/REMC_CARH register).

The carrier signal is generated from these settings as shown in Figure 21.7.1.

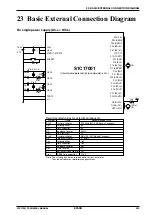

Summary of Contents for S1C17001

Page 1: ...Technical Manual S1C17001 CMOS 16 BIT SINGLE CHIP MICROCONTROLLER ...

Page 33: ...4 POWER SUPPLY VOLTAGE 24 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 63: ...6 INITERRUPT CONTROLLER 54 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 87: ...8 CLOCK GENERATOR CLG 78 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 91: ...9 PRESCALER PSC 82 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 133: ...11 16 BIT TIMER T16 124 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 211: ...16 STOPWATCH TIMER SWT 202 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 219: ...17 WATCHDOG TIMER WDT 210 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 241: ...18 UART 232 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 277: ...20 I2 C 268 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 313: ...25 PACKAGE 304 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...