6 INITERRUPT CONTROLLER

S1C17001 TECHNICAL MANUAL

EPSON

31

6.3 Maskable Interrupt Control

6.3.1 ITC

Enable

To use ITC, set ITEN (D0/ITC_CTL register) to 1.

∗

ITEN: ITC Enable Bit in the ITC Control (ITC_CTL) Register (D0/0x4304)

If ITEN is 0, maskable interrupts will not occur, regardless of the other register settings.

6.3.2 Interrupt Request from Peripheral Module and Interrupt Flag

If an interrupt factor for a permitted interrupt occurs in a peripheral module, that module sends an interrupt request

signal to the ITC. This interrupt request signal causes the corresponding interrupt flag inside the ITC to be set to 1.

The interrupt flag is maintained at 1 until it is reset to 0, indicating that an interrupt request was received from the

peripheral module. The interrupt flag status can be read from the ITC_IFLG register (0x4300).

Table 6.3.2.1 shows the correspondence between interrupt factors and interrupt flags.

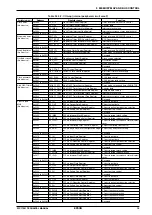

Table 6.3.2.1: Hardware interrupt factors and interrupt flags

Vector No.

Hardware interrupt request

Interrupt flag

4

P0 port interrupt: P00 to P07 port input

EIFT0 (D0/ITC_IFLG register)

5

P1 port interrupt: P10 to P17 port input

EIFT1 (D1/ITC_IFLG register)

6

Stopwatch timer interrupt: 100 Hz/10 Hz/1 Hz signal

EIFT2 (D2/ITC_IFLG register)

7

Clock timer interrupt: 32 Hz/8 Hz/2 Hz/1 Hz signal

EIFT3 (D3/ITC_IFLG register)

8

8-bit OSC1 timer interrupt: Compare match

EIFT4 (D4/ITC_IFLG register)

11

PWM & capture timer interrupt: Compare A/Compare B match

EIFT7 (D7/ITC_IFLG register)

12

8-bit timer interrupt: Timer underflow

IIFT0 (D8/ITC_IFLG register)

13

16-bit timer Ch.0 interrupt: Timer underflow

IIFT1 (D9/ITC_IFLG register)

14

16-bit timer Ch.1 interrupt: Timer underflow

IIFT2 (D10/ITC_IFLG register)

15

16-bit timer Ch.2 interrupt: Timer underflow

IIFT3 (D11/ITC_IFLG register)

16

UART interrupt: Transmit buffer empty/Receive buffer full/Receive error IIFT4 (D12/ITC_IFLG register)

17

Remote controller interrupt: Data length counter underflow/Input rise-

up/Input drop-off

IIFT5 (D13/ITC_IFLG register)

18

SPI interrupt: Transmit buffer empty/Receive buffer full

IIFT6 (D14/ITC_IFLG register)

19

I

2

C interrupt: Transmit buffer empty/Receive buffer full

IIFT7 (D15/ITC_IFLG register)

The ITC generates interrupts to the S1C17 core using the interrupt flags.

If an interrupt flag is set to 1 with the interrupt permitted (refer to next section for details), the ITC sends the inter-

rupt request, interrupt level, and vector number signals to the S1C17 core.

An interrupt flag set to 1 is reset by writing 1. The interrupt flag should be reset to 0 during the interrupt processing

routine. If the interrupt flag is not reset by the interrupt processing routine, the same interrupt will recur after the

interrupt processing routine has ended. (The interrupt is prohibited during interrupt processing and returned to the

permitted state on execution of the reti command after interrupt processing.)

Note however that the interrupt flags (EIFT0 to EIFT7) for interrupts set in the level trigger (refer to Section 6.3.5)

are not reset by writing 1. These interrupt flags are reset when the interrupt source sets the interrupt signal to inac-

tive.

Refer to the interrupt source module section for detailed information on the conditions under which interrupt fac-

tors arise and individual module interrupt settings are made.

Summary of Contents for S1C17001

Page 1: ...Technical Manual S1C17001 CMOS 16 BIT SINGLE CHIP MICROCONTROLLER ...

Page 33: ...4 POWER SUPPLY VOLTAGE 24 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 63: ...6 INITERRUPT CONTROLLER 54 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 87: ...8 CLOCK GENERATOR CLG 78 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 91: ...9 PRESCALER PSC 82 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 133: ...11 16 BIT TIMER T16 124 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 211: ...16 STOPWATCH TIMER SWT 202 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 219: ...17 WATCHDOG TIMER WDT 210 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 241: ...18 UART 232 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 277: ...20 I2 C 268 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 313: ...25 PACKAGE 304 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...