6 INITERRUPT CONTROLLER

32

EPSON

S1C17001 TECHNICAL MANUAL

6.3.3 Interrupt

Permission/Prohibition

Sending an interrupt request to the S1C17 core requires first permitting the individual interrupts using the interrupt

enable bit inside the ITC_EN register (0x4302) corresponding to the interrupt flag. Setting the interrupt enable bit

to 1 permits interrupts, while setting it to 0 (default) prohibits interrupts. The interrupt enable bit does not affect the

interrupt flag. Interrupt flags for interrupt requests generated by a peripheral module will be set regardless of the

interrupt enable bit setting.

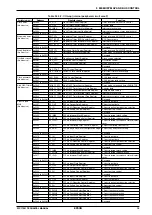

Table 6.3.3.1 shows the correspondence between interrupt enable bits and interrupt flags.

Table 6.3.3.1: Interrupt enable bit list

Vector No.

Hardware interrupt

Interrupt flag

Interrupt enable bit

4

P0 port interrupt

EIFT0 (D0/ITC_IFLG register)

EIEN0 (D0/ITC_EN register)

5

P1 port interrupt

EIFT1 (D1/ITC_IFLG register)

EIEN1 (D1/ITC_EN register)

6

Stopwatch timer interrupt

EIFT2 (D2/ITC_IFLG register)

EIEN2 (D2/ITC_EN register)

7

Clock timer interrupt

EIFT3 (D3/ITC_IFLG register)

EIEN3 (D3/ITC_EN register)

8

8-bit OSC1 timer interrupt

EIFT4 (D4/ITC_IFLG register)

EIEN4 (D4/ITC_EN register)

11

PWM & capture timer interrupt

EIFT7 (D7/ITC_IFLG register)

EIEN7 (D7/ITC_EN register)

12

8-bit timer interrupt

IIFT0 (D8/ITC_IFLG register)

IIEN0 (D8/ITC_EN register)

13

16-bit timer Ch.0 interrupt

IIFT1 (D9/ITC_IFLG register)

IIEN1 (D9/ITC_EN register)

14

16-bit timer Ch.1 interrupt

IIFT2 (D10/ITC_IFLG register)

IIEN2 (D10/ITC_EN register)

15

16-bit timer Ch.2 interrupt

IIFT3 (D11/ITC_IFLG register)

IIEN3 (D11/ITC_EN register)

16

UART interrupt

IIFT4 (D12/ITC_IFLG register)

IIEN4 (D12/ITC_EN register)

17

Remote controller interrupt

IIFT5 (D13/ITC_IFLG register)

IIEN5 (D13/ITC_EN register)

18

SPI interrupt

IIFT6 (D14/ITC_IFLG register)

IIEN6 (D14/ITC_EN register)

19

I

2

C interrupt

IIFT7 (D15/ITC_IFLG register)

IIEN7 (D15/ITC_EN register)

Note: • To prevent generating unnecessary interrupts, always set the interrupt flags before

permitting interrupts by writing 1 to the interrupt enable bit.

• To generate an actual interrupt, the IE bit in the S1C17 core Processor Status Register (PSR)

must be set to 1, in addition to the interrupt enable bit. The S1C17 core will not accept

maskable interrupt requests if the IE bit is set to 0. In this case, interrupt requests from the

ITC will be retained and accepted after the IE bit is set to 1.

Summary of Contents for S1C17001

Page 1: ...Technical Manual S1C17001 CMOS 16 BIT SINGLE CHIP MICROCONTROLLER ...

Page 33: ...4 POWER SUPPLY VOLTAGE 24 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 63: ...6 INITERRUPT CONTROLLER 54 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 87: ...8 CLOCK GENERATOR CLG 78 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 91: ...9 PRESCALER PSC 82 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 133: ...11 16 BIT TIMER T16 124 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 211: ...16 STOPWATCH TIMER SWT 202 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 219: ...17 WATCHDOG TIMER WDT 210 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 241: ...18 UART 232 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 277: ...20 I2 C 268 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 313: ...25 PACKAGE 304 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...