S1C63656 TECHNICAL MANUAL

EPSON

141

CHAPTER 5: SUMMARY OF NOTES

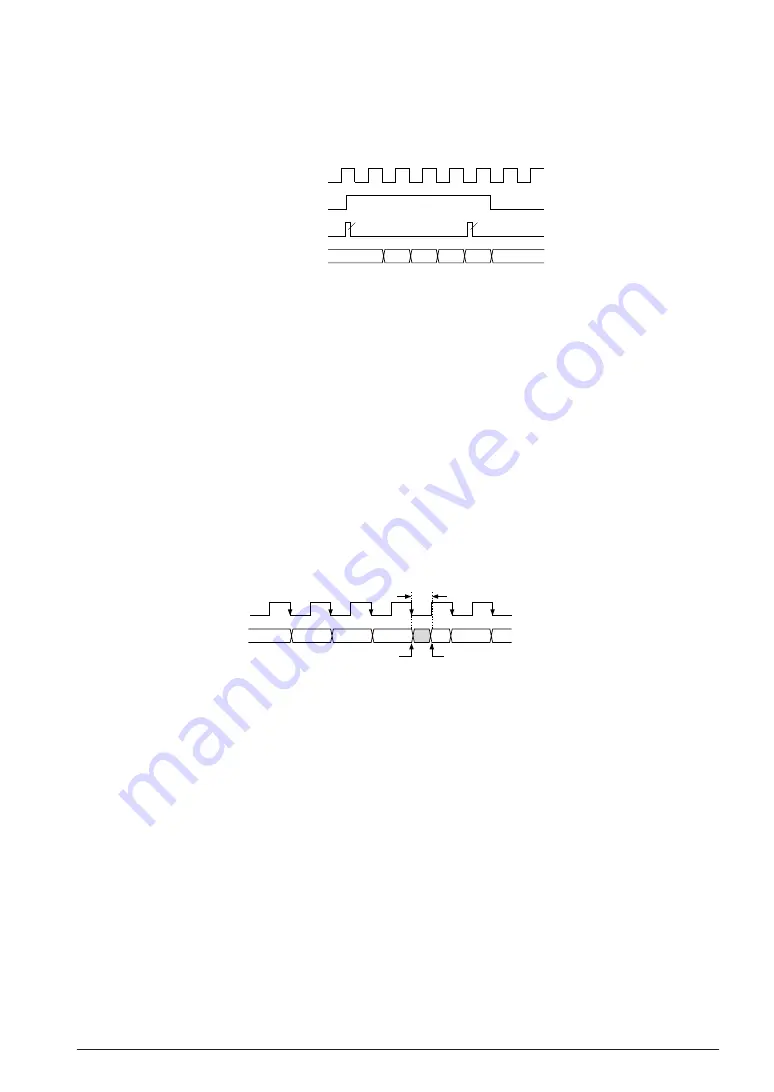

(2) The programmable timer actually enters RUN/STOP status in synchronization with the falling edge

of the input clock after writing to the PTRUNx register. Consequently, when "0" is written to the

PTRUNx register, the timer enters STOP status at the point where the counter is decremented (-1).

The PTRUNx register maintains "1" for reading until the timer actually stops.

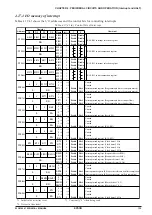

Figure 5.2.1 shows the timing chart for the RUN/STOP control.

PTRUNx (WR)

PTDx0–PTDx7

42H

41H 40H 3FH 3EH

3DH

PTRUNx (RD)

Input clock

"1" (RUN)

writing

"0" (STOP)

writing

Fig. 5.2.1 Timing chart for RUN/STOP control

It is the same even in the event counter mode. Therefore, be aware that the counter does not enter

RUN/STOP status if a clock is not input after setting the RUN/STOP control register (PTRUN0).

(3) Since the TOUT signal is generated asynchronously from the PTOUT register, a hazard within 1/2

cycle is generated when the signal is turned on and off by setting the register.

(4) When the OSC3 oscillation clock is selected for the clock source, it is necessary to turn the OSC3

oscillation ON, prior to using the programmable timer. However the OSC3 oscillation circuit requires

a time at least 5 msec from turning the circuit ON until the oscillation stabilizes. Therefore, allow an

adequate interval from turning the OSC3 oscillation circuit ON to starting the programmable timer.

Refer to Section 4.3, "Oscillation Circuit", for the control and notes of the OSC3 oscillation circuit.

At initial reset, the OSC3 oscillation circuit is set in the off state.

(5) For the reason below, pay attention to the reload data write timing when changing the interval of the

programmable timer interrupts while the programmable timer is running.

The programmable timer counts down at the falling edge of the input clock and at the same time it

generates an interrupt if the counter underflows. Then it starts loading the reload data to the counter

and the counter data is determined at the next rising edge of the input clock (period shown in as

➀

in

the figure).

Input clock

Counter data

(continuous mode)

(Reload data = 25H)

03H

02H

01H

00H

25H

24H

Counter data is determined by reloading.

Underflow (interrupt is generated)

➀

Fig. 5.2.2 Reload timing for programmable timer

To avoid improper reloading, do not rewrite the reload data after an interrupt occurs until the counter

data is determined including the reloading period

➀

. Be especially careful when using the OSC1 (low-

speed clock) as the clock source of the programmable timer and the CPU is operating with the OSC3

(high-speed clock).

Serial interface

(1) Perform data writing/reading to the data registers SD0–SD7 only while the serial interface is not

running (i.e., the synchronous clock is neither being input or output).

(2) As a trigger condition, it is required that data writing or reading on data registers SD0–SD7 be

performed prior to writing "1" to SCTRG. (The internal circuit of the serial interface is initiated

through data writing/reading on data registers SD0–SD7.) In addition, be sure to enable the serial

interface with the ESIF register before setting the trigger.

Supply trigger only once every time the serial interface is placed in the RUN state. Refrain from

performing trigger input multiple times, as leads to malfunctioning. Moreover, when the synchronous

clock SCLK is external clock, start to input the external clock after the trigger.

(3) Setting of the input/output permutation (MSB first/LSB first) with the SDP register should be done

before setting data to SD0–SD7.

(4) Be aware that the maximum clock frequency for the serial interface is limited to 1 MHz when OSC3 is

used as the clock source of the programmable timer or in the slave mode.