Page 36

Epson Research and Development

Vancouver Design Center

S1D13503

Hardware Functional Specification

X18A-A-001-08

Issue Date: 01/01/29

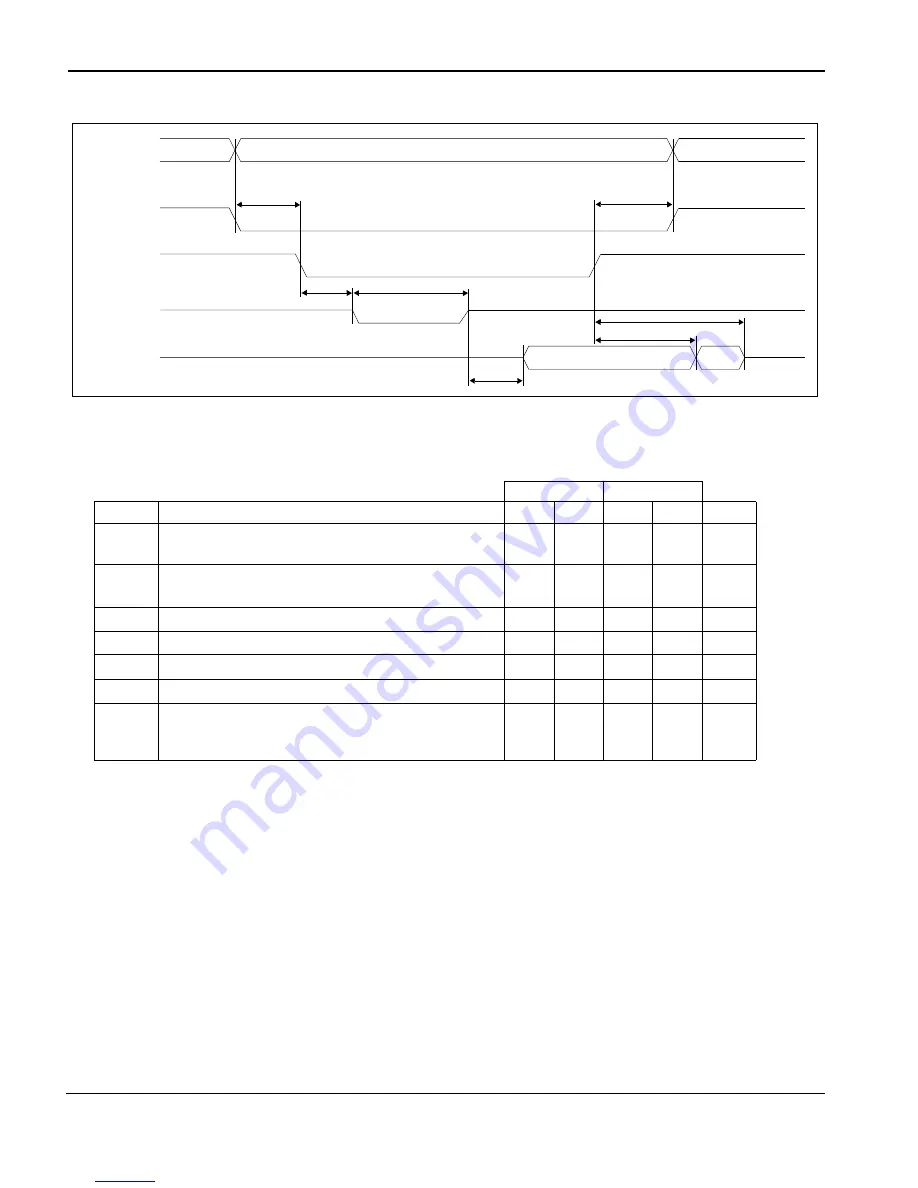

MEMR# Timing

Figure 17: MEMR# Timing (Non-MC68000)

Where MCLK period = 1/f

OSC

, or 2/f

OSC

, or 4/f

OSC

depending on which display mode the chip is in. (See section 9.2 and

9.3.)

Table 7-8: MEMR# Timing (Non-MC68000)

3V/3.3V

5V

Symbol

Parameter

Min

Max

Min

Max

Units

t1

AB[19:0], BHE# and MEMCS# valid before MEMR#

falling edge

0

0

ns

t2

AB[19:0], BHE# and MEMCS# hold from MEMR#

rising edge

0

0

ns

t3

MEMR# falling edge to READY falling edge

30

20

ns

t4

READY rising edge to DB[15:0] valid

15

10

ns

t5

DB[15:0] hold from MEMR# rising edge

20

10

ns

t6

MEMR# rising edge to DB[15:0] hi-z delay

30

20

ns

t7

READY negated pulse width

3.5*

MCLK

+ 20

3.5*

MCLK

+ 10

ns

AB[19:0]

MEMCS#

MEMR#

READY

VALID

VALID

t1

t3

t7

t5

t2

t6

t4

DB[15:0]

BHE#

Hi-Z

Hi-Z

Hi-Z

Hi-Z

electronic components distributor