Page 98

Epson Research and Development

Vancouver Design Center

S1D13504

Hardware Functional Specification

X19A-A-002-19

Issue Date: 01/11/06

REG[0Eh] bits 7-0

Screen 1 Line Compare Bits [9:0]

REG[0Fh] bits 1-0

In split screen mode, the panel is divided into screen 1 and screen 2, with screen 1 above screen 2.

These registers form a 10-bit value that specify the screen 1 size in 1-line resolution. The maximum

screen 1 vertical size is 1024 lines. Screen 2 is visible only if the screen 1 line compare is less than

the vertical panel size. The starting address for screen 1 is given by the Screen 1 Display Start

Address registers (REG[10h], REG[11h], REG[12h]). The starting address for screen 2 is given by

the Screen 2 Display Start Address registers (REG[13h], REG[14h], REG[15h]).

For normal operation (no split screen):

this register must be set greater than the vertical display height REG[08h] and REG[09h]

(e.g. set to 3FFh).

For split screen on a single panel:

Split screen 1 vertical size in number of lines = (ContentsOfThisRegister) + 1

For split screen on a dual panel:

Split screen 1 vertical size in number of lines = (ContentsOfThisRegister) + 1,

if (ContentsOfThisRegister)

≤

00EFh

or

Split screen 1 vertical size in number of lines = (ContentsOfThisRegister) + 2,

if (ContentsOfThisRegister)

>

00EFh

Note

For further details, see Section 10.2, “Image Manipulation” on page 117 and the S1D13504 Pro-

gramming Notes and Examples, document number X19A-G-002-xx.

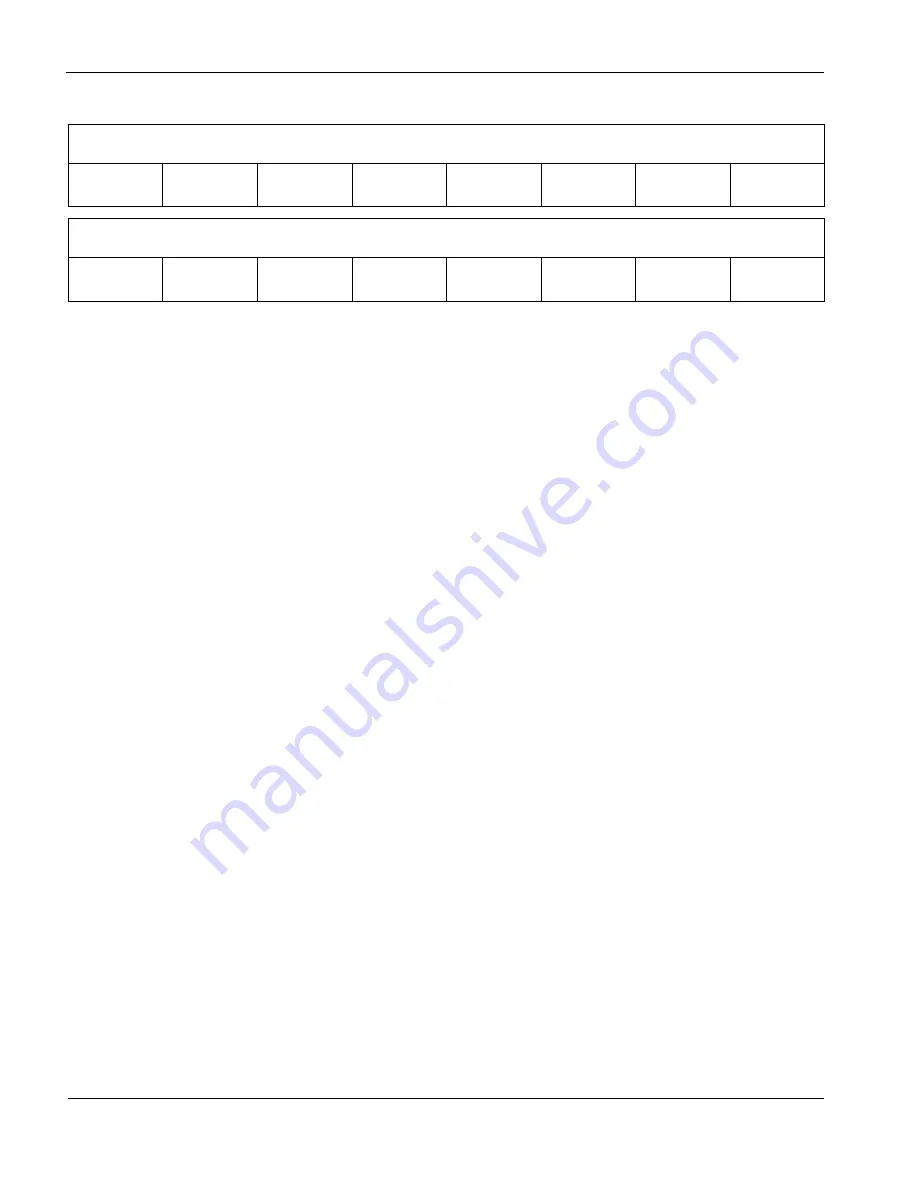

Screen 1 Line Compare Register 0

REG[0Eh]

RW

Screen 1 Line

Compare Bit 7

Screen 1 Line

Compare Bit 6

Screen 1 Line

Compare Bit 5

Screen 1 Line

Compare Bit 4

Screen 1 Line

Compare Bit 3

Screen 1 Line

Compare Bit 2

Screen 1 Line

Compare Bit 1

Screen 1 Line

Compare Bit 0

Screen 1 Line Compare Register 1

REG[0Fh]

RW

n/a

n/a

n/a

n/a

n/a

n/a

Screen 1 Line

Compare Bit 9

Screen 1 Line

Compare Bit 8