Epson Research and Development

Page 115

Vancouver Design Center

Hardware Functional Specification

S1D13504

Issue Date: 01/11/06

X19A-A-002-19

10 Display Configuration

10.1 Display Mode Data Format

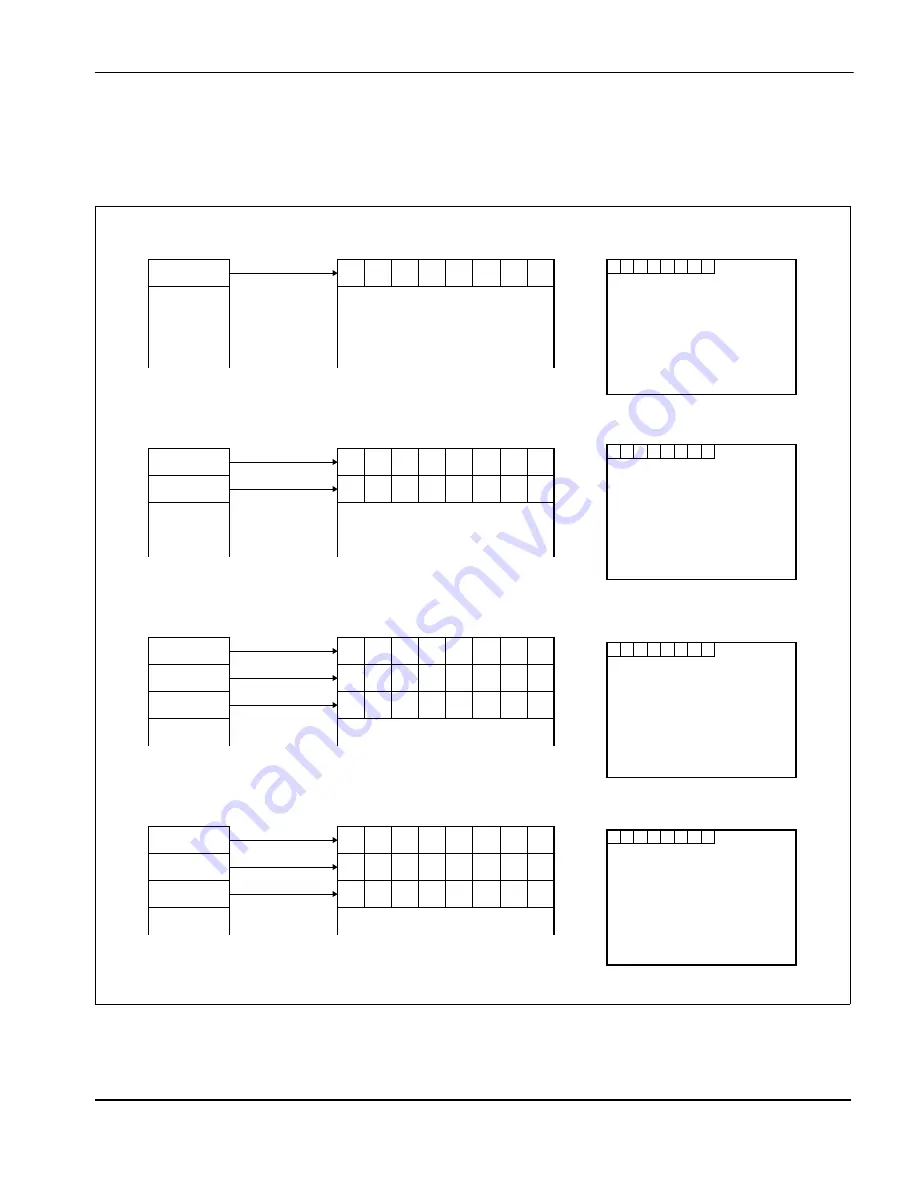

Figure 10-1: 1/2/4/8 Bit-Per-Pixel Format Memory Organization

1-bpp:

A

0

A

1

A

2

A

3

A

4

A

5

A

6

A

7

Host Address

Display Buffer

Panel Display

P

0

P

1

P

2

P

3

P

4

P

5

P

6

P

7

2-bpp:

A

0

B

0

A

1

B

1

A

2

B

2

A

3

B

3

Host Address

Display Buffer

A

4

B

4

A

5

B

5

A

6

B

6

A

7

B

7

bit 7

bit 0

bit 7

bit 0

4-bpp:

A

0

B

0

C

0

D

0

A

1

B

1

C

1

D

1

Host Address

Display Buffer

A

2

B

2

C

2

D

2

A

3

B

3

C

3

D

3

bit 7

bit 0

A

4

B

4

C

4

D

4

A

5

B

5

C

5

D

5

Host Address

Display Buffer

bit 7

bit 0

8-bpp:

3-3-2 RGB

R

0

2

R

0

1

R

0

0

G

0

2

G

0

1

G

0

0

B

0

1

B

0

0

R

1

2

R

1

1

R

1

0

G

1

2

G

1

1

G

1

0

B

1

1

B

1

0

R

2

2

R

2

1

R

2

0

G

2

2

G

2

1

G

2

0

B

2

1

B

2

0

Byte 0

Byte 0

Byte 1

Byte 0

Byte 1

Byte 2

Byte 0

Byte 1

Byte 2

Panel Display

P

0

P

1

P

2

P

3

P

4

P

5

P

6

P

7

Panel Display

P

0

P

1

P

2

P

3

P

4

P

5

P

6

P

7

Panel Display

P

0

P

1

P

2

P

3

P

4

P

5

P

6

P

7

P

n

= (A

n

)

P

n

= (A

n

, B

n

)

P

n

= (A

n

, B

n

, C

n

, D

n

)

P

n

= (R

n

2-0

, G

n

2-0

, B

n

1-0

)