Page 10

Epson Research and Development

Vancouver Design Center

S1D13504

Programming Notes and Examples

X19A-G-002-07

Issue Date: 01/02/01

2.2.2 Initialization Example

This section presents an example of how to initialize the S1D13504 registers.

Example 1: Initialize the registers for a 16 color 640x480 dual passive LCD using a 16 bit

data interface; assume 2M byte of display buffer.

Program the S1D13504 registers in the following order with the data supplied. Note that for this

example, it is assumed that the arrays “unsigned char RED[16], GREEN[16], BLUE[16]” are

defined and initialized for the required colors. For example, RED[2], GREEN[2], and BLUE[2] refer

to the color components of pixel value 2.

In addition, it is assumed that there is no external RAMDAC since only the LCD is being

programmed. Consequently, the RAMDAC registers are not programmed.

For code examples, see Section 9, “Sample Code” on page 54.

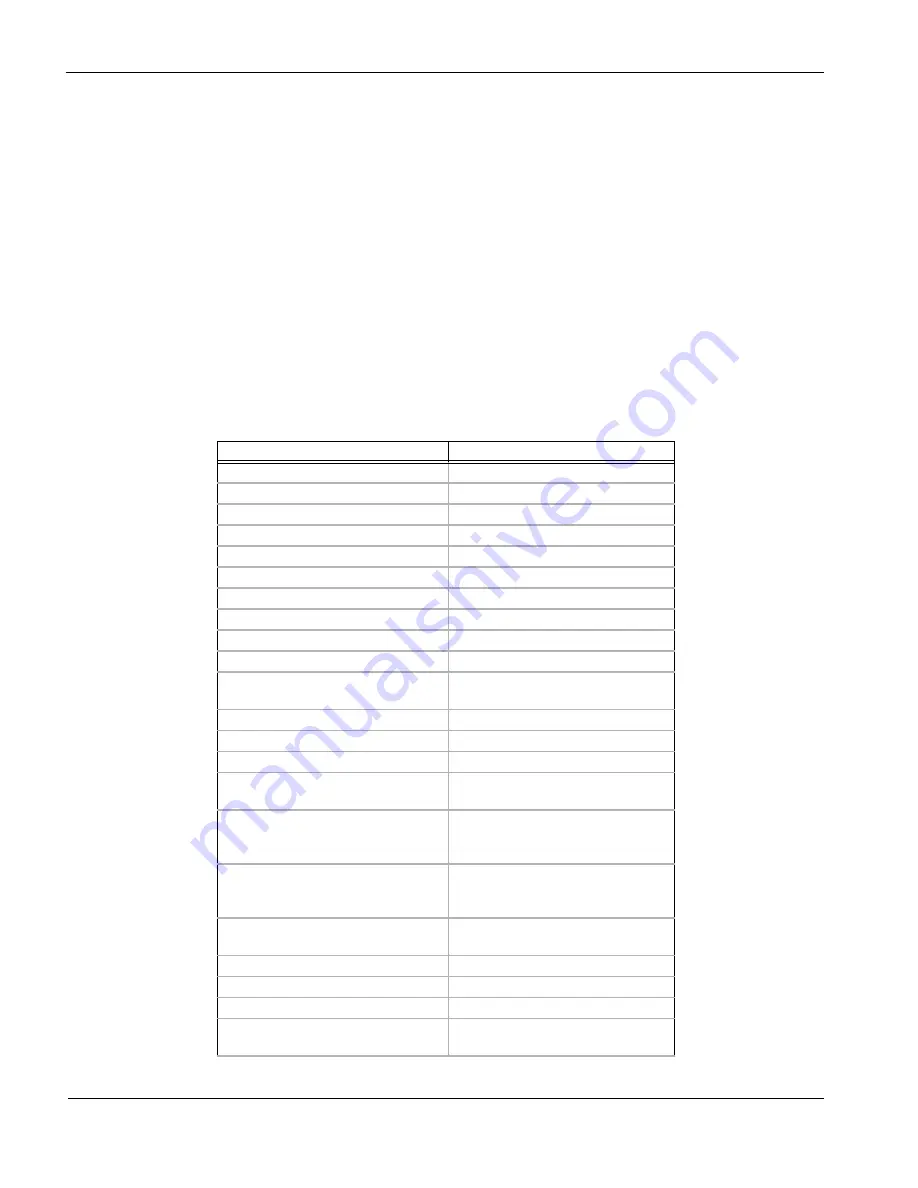

Table 2-1: Initializing the S1D13504 Registers

Operation

Description

REG[1Bh] = 0x00

Enable Host Interface

REG[23h] = 0x80

Disable the Display FIFO

REG[01h] = 0x30

Set Memory Type

REG[22h] = 0x24

Set Performance Register

REG[02h] = 0x26

Set Dual/Single Panel

REG[03h] = 0x00

MOD Rate

REG[04h] = 0x4F

Horizontal Display Width

REG[05h] = 0x1F

Horizontal Non-Display Period

REG[06h] = 0x00

HSYNC Start Position

REG[07h] = 0x00

HSYNC Pulse Width

REG[08h] = 0xEF

REG[09h] = 0x00

Vertical Display Height

REG[0Ah] = 0x01

Vertical Non-Display Period

REG[0Bh] = 0x00

VSYNC Start Position

REG[0Ch] = 0x00

VSYNC Pulse Width

REG[0Eh] = 0xFF

REG[0Fh] = 0x03

Screen 1 Line Compare

REG[10h] = 0x00

REG[11h] = 0x00

REG[12h] = 0x00

Screen 1 Display Start Address

REG[13h] = 0x00

REG[14h] = 0x00

REG[15h] = 0x00

Screen 2 Display Start Address

REG[16h] = 0xA0

REG[17h] = 0x00

Memory Address Offset

REG[18h] = 0x00

Pixel Panning

REG[19h] = 0x01

Clock Configuration

REG[1Ah] = 0x00

Power Save Configuration

REG[1Eh] = 0x00

REG[1Fh] = 0x00

General I/O Configuration