Page 24

Epson Research and Development

Vancouver Design Center

S1D13504

Programming Notes and Examples

X19A-G-002-07

Issue Date: 01/02/01

4.1.1 Registers

Registers [16h] and [17h] form a ten bit value referred to as the memory offset. This offset is the

number of words from the first byte of one line of display buffer to the first byte in the next line. This

value takes into account the number of non-displayed pixels on each line.

Different color depths have different numbers of pixels per word. To represent an offset of a given

number of pixels the offset registers will contain different values at different color depths. The

formula to calculate the offset to write to these registers is:

offset_register = pixels_per_line / pixels_per_word

4.1.2 Examples

Example 2: Determine the offset value required for 800 pixels at a color depth of 8 bpp.

A color depth of 8 bpp means each pixel requires one byte therefore each word contains two pixels.

offset = pixels_per_line / pixels_per_word = 800 / 2 = 400 = 0x190 words

Register [17h] would be set to 0x01 and register [16h] would be set to 0x90.

Example 3: Program the Memory Address Offset Registers to support a 16 color (4 bpp)

640x480 virtual display on a 320x240 LCD panel.

To create a virtual display the offset registers must be programmed to the horizontal size of the larger

“virtual” image. After determining the amount of memory used by each line, do a calculation to see

if there is enough memory to support the desired number of lines.

1.

Initialize the S1D13504 registers for a 320x240 panel. (See Section 2.2, “Register Initialization” on

page 9).

2.

Determine the number of words required per line (the offset). In this case we want a width of

640 pixels and there are four pixels to every word.

offset = pixels_per_line / pixels_per_word = 640 / 4 = 160 words = 0xA0 words

3.

Check that we have enough memory for the required virtual height.

Each line uses 160 words and we need 480 lines (160*480) for a total of 76,800 words, less than

the minimum supported memory size of 512K bytes. It is safe to continue with these values.

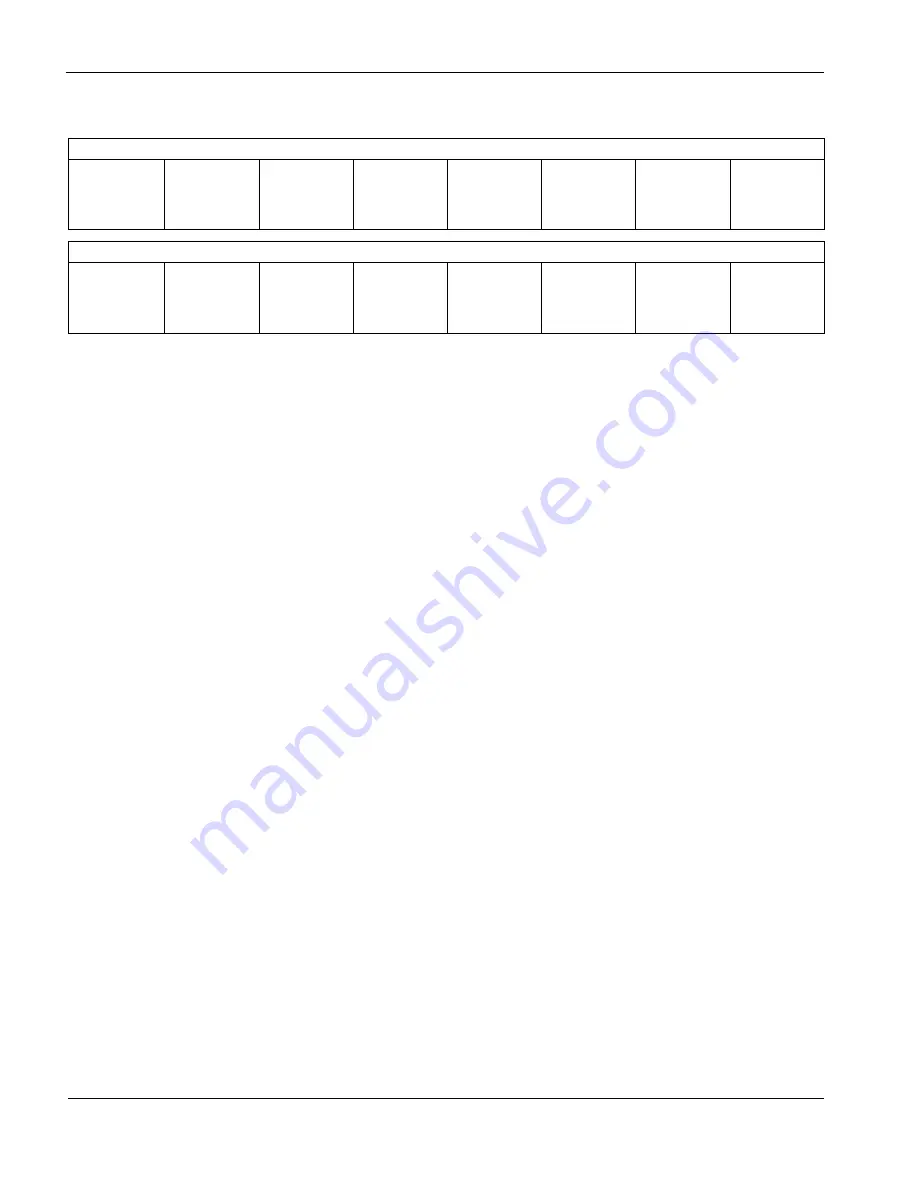

REG[16h] Memory Address Offset Register 0

Memory

Address

Offset

Bit 7

Memory

Address

Offset

Bit 6

Memory

Address

Offset

Bit 5

Memory

Address

Offset

Bit 4

Memory

Address

Offset

Bit 3

Memory

Address

Offset

Bit 2

Memory

Address

Offset

Bit 1

Memory

Address

Offset

Bit 0

REG[17h] Memory Address Offset Register 1

n/a

n/a

n/a

n/a

n/a

n/a

Memory

Address

Offset

Bit 9

Memory

Address

Offset

Bit 8