Page 34

Epson Research and Development

Vancouver Design Center

S1D13504

Programming Notes and Examples

X19A-G-002-07

Issue Date: 01/02/01

6.1.2 Simultaneous Display

For Simultaneous Display, only 4/8-bit single passive LCD panels and 9-bit active matrix TFT

panels can be used. Simultaneous Display requires that the panel timing be taken from the CRT

timing registers and thereby limits the number of useful modes supported.

The configuration of both CRT and panel must not violate the limitations as described in “Frame

Rate Calculation” (Chapter 11) of the S1D13504 Hardware Functional Specification. For example,

on a 640x480 single panel, the maximum values of both the panel pixel clock and CRT frame rate

are 40 MHz and 85 Hz respectively. When pixel depth is less than 8 bpp, the RAMDAC is

programmed with the same values as the Look-Up Table. The S1D13504 does not support Simulta-

neous Display in a color depth greater than 8 bpp.

When color depth is 8 bpp, the RAMDAC should be programmed to mimic the recommended values

in the Look-Up Table as described in Section 3.3.2. The recommendation is that the intensities of

the three prime colors (RGB) be distributed evenly. Table 6-3 shows the recommended RAMDAC

palette data for 8 bpp Simultaneous Display. Table 6-4 shows the related register data for some

possible CRT options with an 8-bit Color 640X480 single passive panel.

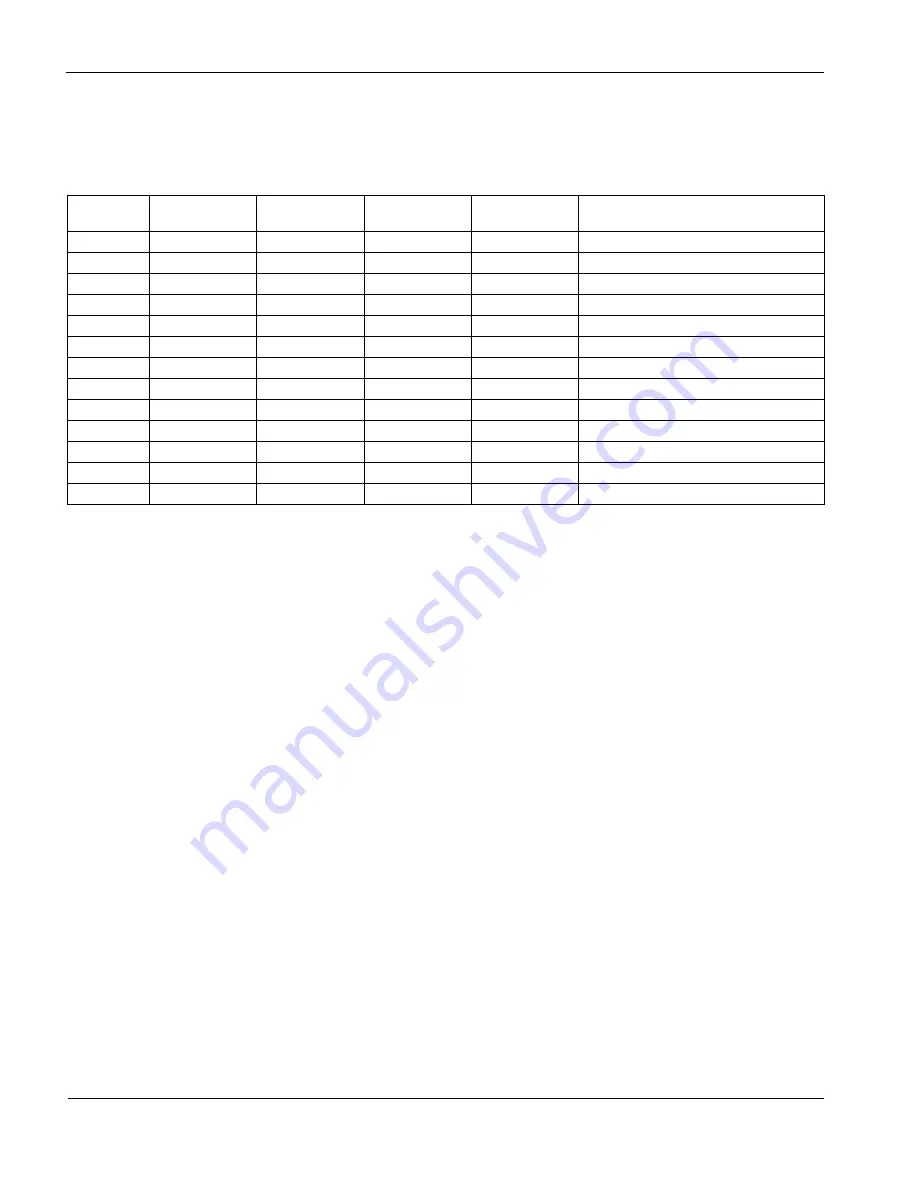

Table 6-2: Related Register Data for CRT Only

Register

640X480@60Hz

PCLK=25.175MHz

640X480@75Hz

PCLK=31.500MHz

800X600@56Hz

PCLK=36.0 MHz

800X600@60Hz

PCLK=40.0 MHz

Notes

REG[04h]

0100 1111

0100 1111

0110 0011

0110 0011

set horizontal display width

REG[05h]

0001 0011

0001 1000

0001 1011

0001 1111

set horizontal non-display period

REG[06h]

0000 0001

0000 0001

0000 0010

0000 0100

set HSYNC start position

REG[07h]

0000 1011

0000 0111

1000 1000

1000 1111

set HSYNC polarity and pulse width

REG[08h]

1101 1111

1101 1111

0101 0111

0101 0111

set vertical display height bits 7-0

REG[09h]

0000 0001

0000 0001

0000 0010

0000 0010

set vertical display height bits 9-8

REG[0Ah]

0010 1100

0001 0011

0001 1000

0001 1011

set vertical non-display period

REG[0Bh]

0000 1001

0000 0000

0000 0000

0000 0000

set VSYNC start position

REG[0Ch]

0000 0001

0000 0010

1000 0001

1000 0011

set VSYNC polarity and pulse width

REG[0Dh]

0000 1110

0000 1110

0000 1110

0000 1110

set 8 bpp and CRT enable

REG[19h]

0000 0000

0000 0000

0000 0000

0000 0000

set MCLK and PCLK divide

REG[2Ch]

0000 0000

0000 0000

0000 0000

0000 0000

set write mode address to 0

REG[2Eh]

load RAMDAC palette data