Epson Research and Development

Page 37

Vancouver Design Center

Programming Notes and Examples

S1D13504

Issue Date: 01/02/01

X19A-G-002-07

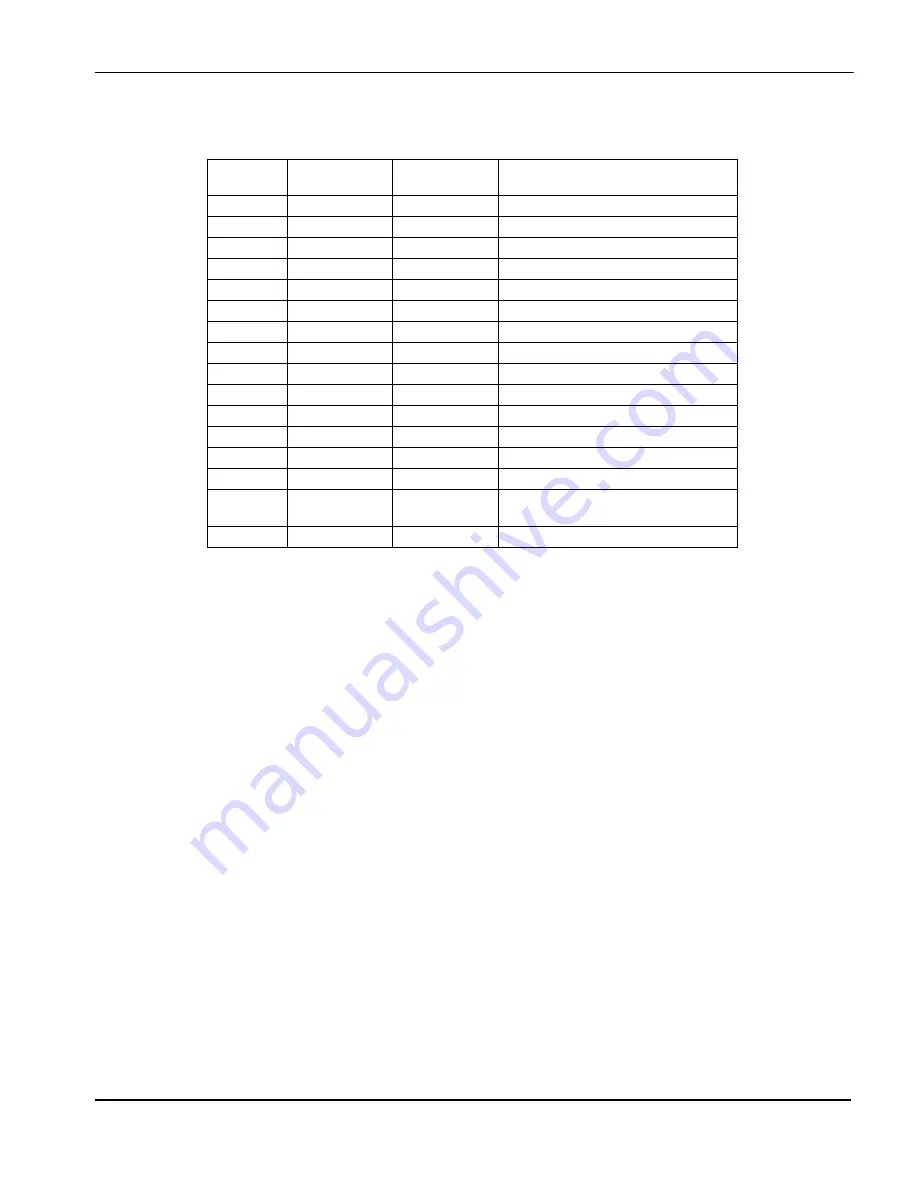

Table 6-4: Related register data for Simultaneous Display

Register

640X480@75Hz

PCLK=40.0MHz

640X480@60Hz

PCLK=40.0MHz

Notes

REG[04h]

0100 1111

0100 1111

set horizontal display width

REG[05h]

0001 1101

0001 0011

set horizontal non-display period

REG[06h]

0000 0011

0000 0001

set HSYNC start position

REG[07h]

0000 0111

0000 1011

set HSYNC polarity and pulse width

REG[08h]

1000 1111

1101 1111

set vertical display height bits 7-0

REG[09h]

0000 0001

0000 0001

set vertical display height bits 9-8

REG[0Ah]

0010 1100

0010 1100

set vertical non-display period

REG[0Bh]

0000 0000

0000 1001

set VSYNC start position

REG[0Ch]

1000 0010

0000 0001

set VSYNC polarity and pulse width

REG[0Dh]

0000 1111

0000 1111

set 8 bpp and CRT enable

REG[19h]

0000 0000

0000 0000

set MCLK and PCLK divide

REG[24h]

0000 0000

0000 0000

set look-up table address to 0

REG[26h]

load look-up table

REG[27h]

0000 0000

0000 0000

set look-up table to bank 0

REG[2Ch]

program

RAMDAC

program

RAMDAC

set write mode address to 0

REG[2Eh]

load RAMDAC palette data