Page 16

Epson Research and Development

Vancouver Design Center

S1D13504

Hardware Functional Specification

X19A-A-002-19

Issue Date: 01/11/06

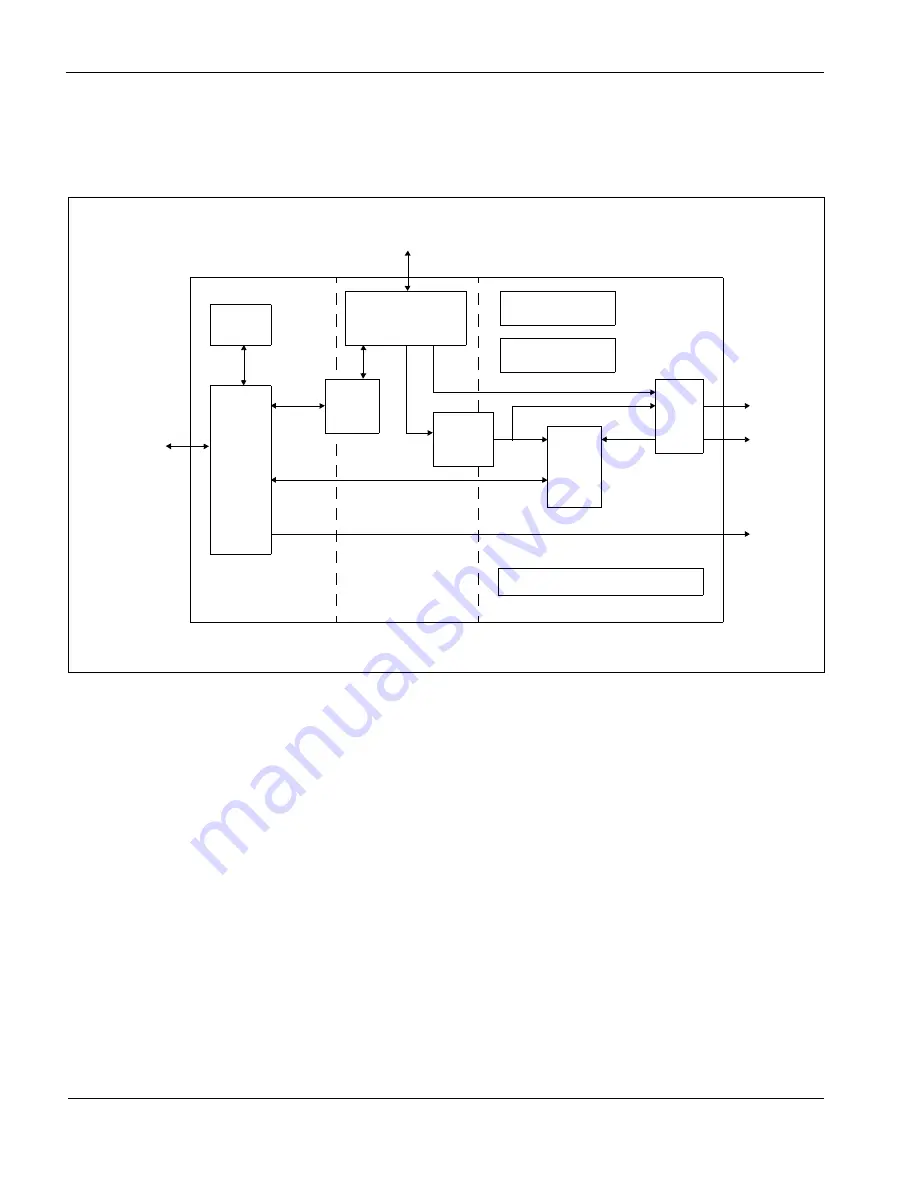

4 Block Description

4.1 Functional Block Diagram

Figure 4-1: System Block Diagram Showing Datapaths

LCD

Memory

Controller

16-bit FPM/EDO

DRAM

LCD

Clocks

Power Save

Register

CRTC

Look-Up

I/F

CPU / MPU

Host

I/F

DAC

CPU

R/W

Bus Clock

Memory Clock

Pixel Clock

Display

FIFO

Control

DAC

Data

Table