Epson Research and Development

Page 13

Vancouver Design Center

S5U13504B00C Rev.1.0 ISA Bus Evaluation Board User Manual

S1D13504

Issue Date: 01/02/02

X19A-G-004-06

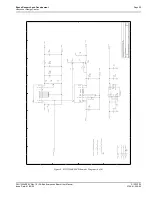

6 Technical Description

6.1 ISA Bus Support

The S5U13504B00C directly supports the 16-bit ISA bus environment. All the configuration options

[MD15:0] are either hard-wired or selectable through the five-position DIP Switch S1. Refer to

Table 2-1 “Configuration DIP Switch Settings,” on page 8 for details.

Note

1. The 8-bit ISA bus is not supported by the S5U13504B00C board design.

2. The S1D13504 is a memory-mapped device with 2M bytes of linear addressed display buffer

memory as well as a separate 37 byte register space. On the S5U13504B00C, the S1D13504

registers have been mapped to a start-address of C00000h and the 2M byte display buffer has

been mapped to a start-address of E00000h.

3. When using this board in a PC environment, system memory must be limited to 12M bytes as

more than this will conflict with the S1D13504 display buffer/register addresses.

Note

Due to backwards compatibility with the S5U13504B00B Evaluation Board, which supports

both an 8 and a 16-bit CPU interface, third party software must perform a write to address

D00000h to enable a 16-bit ISA environment. This must be done prior to initializing the

S1D13504. Failure to do so will result in the S1D13504 being configured as a 16-bit device (de-

fault, power-up), with the ISA Bus interface (supported through the PAL (U4)) configured for an

8-bit interface.

The Epson supplied software performs this function automatically.