Epson Research and Development

Page 23

Vancouver Design Center

S5U13504B00C Rev.1.0 ISA Bus Evaluation Board User Manual

S1D13504

Issue Date: 01/02/02

X19A-G-004-06

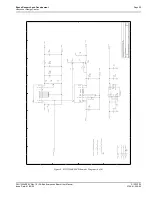

Figure 4: S1D13504B00C Schematic Diagram (4 of 6)

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

A

A

B

B

C

C

D

D

PLACE

CLOSE TO RAMDAC AVCC

PINS

1.0

S

5

U

135

04B

00C

IS

A

-B

u

s

R

e

v.

1.0 E

v

al

ua

ti

on

B

oar

d

B

46

T

ues

d

a

y,

S

e

ptembe

r 3

0

, 1997

S

iz

e

D

o

c

u

ment N

u

mber

R

e

v

D

a

te:

S

he

et

of

SD

0

SD

1

F

P

D

A

T

1

5

SD

2

F

P

D

A

T

1

4

SD

3

F

P

D

A

T

1

3

SD

4

F

P

D

A

T

1

2

SD

5

F

P

D

A

T

1

1

SD

6

F

P

D

A

T

1

0

SD

7

F

P

D

A

T

9

FP

D

A

T[

8

..

1

5

]

S

D

[0..

15]

DA

C

P

0

AV

C

C

AV

C

C

AV

C

C

VC

C

AV

C

C

AV

C

C

IO

V

D

D

+1

2

V

VC

C

VS

S

3.3V

R2

7

182

1%

C2

1

.1

R2

6

1K

L1

F

E

RRI

T

E

B

E

A

D

F

A

I

R

-R

IT

E

27430

01111

F

E

R

R

O

X

C

U

B

E

V

K

2

0

019-

4B

P

H

ILL

IP

S

4312

0203669

0

1

2

C1

9

10uF

T

antul

um

+

J5

6

1

11

7

2

12

8

3

13

9

4

14

10

5

15

L3

1

2

L4

1

2

L5

1

2

R1

7

39

R2

0

3

9

R2

1

3

9

R2

2

39

R2

3

150

1%

R2

4

150

1%

R2

5

150

1%

D4

1N

4148

2

1

D5

2

1

D6

2

1

D1

1N

4148

2

1

D2

2

1

D3

2

1

C1

5

.01

C1

6

.01

C1

7

.01

C1

8

.01

R1

8

10K

R1

9

10K

R2

8

3

9

R2

9

39

U6

B

T

4

81A

D0

8

D1

9

D2

10

D3

11

D4

12

D5

13

D6

14

D7

15

/RD

6

/W

R

16

RS

0

17

RS

1

18

RS

2

19

P0

32

P1

33

P2

34

P3

35

P4

36

P5

37

P6

38

P7

39

CL

K

40

CO

M

P

29

VR

E

F

31

IRE

F

28

RE

D

25

GR

E

E

N

26

BL

U

E

27

OL

0

41

OL

1

42

OL

2

43

OL

3

44

/S

Y

N

C

5

/B

L

A

NK

7

SE

T

U

P

23

OP

A

30

AV

C

C

4

/T

R

U

E

C

O

L

20

AV

C

C

21

AV

C

C

22

GN

D

3

GN

D

24

/S

E

N

S

E

1

6*

/8

2

C2

0

.1

D7

LM38

5B

Z

-1.2

1

2

3

L2

1

2

D

A

CRS

0

D

A

CRS

1

BL

A

N

K#

D

A

CW

R#

D

A

CRD#

D

A

CCL

K

F

P

D

A

T

[8..15]

S

D

[0..15

]

DA

C

P

0

HR

T

C

VR

T

C

GN

D

VC

C

+

12V

3.

3

V

E

P

S

O

N

RE

S

E

A

RCH A

ND DE

V

E

L

O

P

M

E

N

T

, INC

.