Page 14

Epson Research and Development

Vancouver Design Center

S1D13504

Interfacing to the NEC VR4102™ Microprocessor

X19A-G-007-08

Issue Date: 01/10/26

4.3 NEC V

R

4102™ Configuration

The NEC V

R

4102™ provides the internal address decoding necessary to map to an external

LCD controller. Physical address 0A00 0000h to 0AFF FFFFh (16M bytes) is reserved for

an external LCD controller.

The S1D13504 supports up to 2M bytes of display buffer. The NEC V

R

4102™ address line

A21 is used to select between the S1D13504 display buffer and internal register set.

The V

R

4102™ uses a read, write and system high-byte enable to interface to an external

LCD controller. The S1D13504 uses low and high byte read and write strobes and therefore

minimal “glue” logic is necessary.

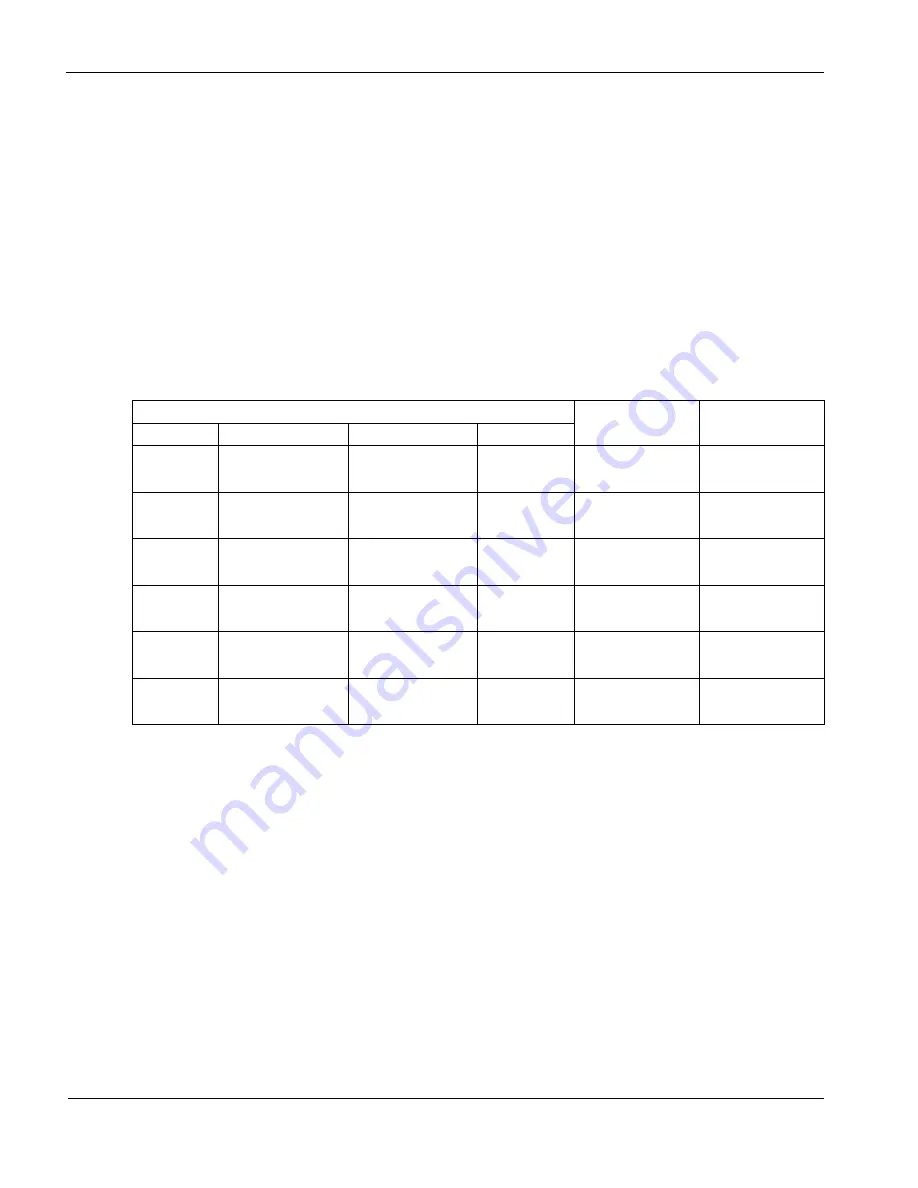

Table 4-2: NEC/S1D13504 Truth Table

NEC Signals

Cycle

S1D13504 Signals

SHB#

RD#

WR#

A0

1

0

1

0

8-bit even address

Read

RD0# = low

RD1# = high

1

0

1

1

8-bit odd address

Read

RD0# = high

RD1# - low

0

0

1

x

16-bit Read

RD0# = low

RD1# - low

1

1

0

0

8-bit even address

Write

WR0# = low

WR1# = high

1

1

0

1

8-bit odd address

Write

WR0# = high

WR1# = low

0

1

0

x

16-bit Write

WR0# = low

WR1# = low