Epson Research and Development

Page 13

Vancouver Design Center

Interfacing to the Motorola MCF5307 "Coldfire" Microprocessor

S1D13504

Issue Date: 01/02/02

X19A-G-011-07

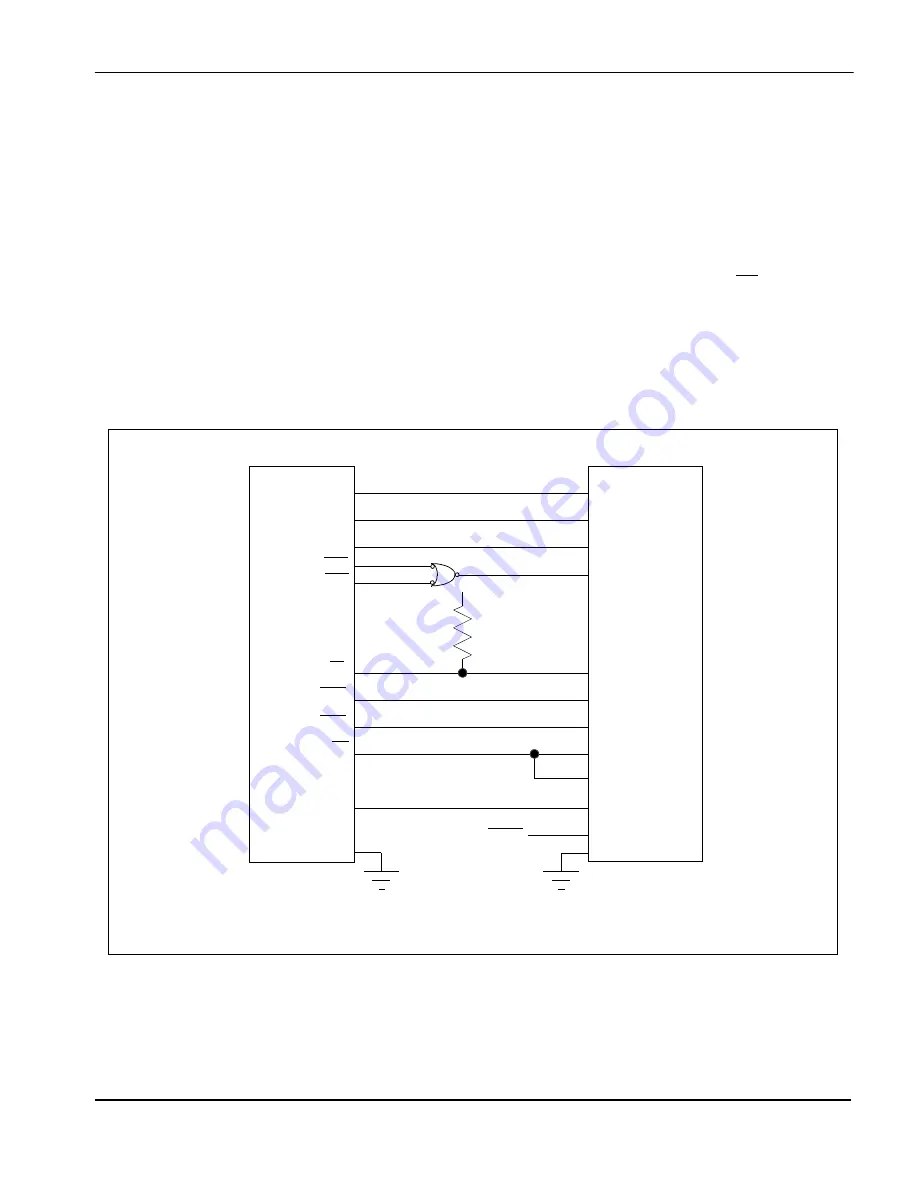

4 MCF5307 To S1D13504 Interface

4.1 Hardware Connections

The interface between the S1D13504 and the MCF5307 requires minimal glue logic. Since

the S1D13504 has a single chip select input for both display RAM and registers, a single

external gate is required to produce a negative-OR function of the two MCF5307 chip

selects. A single resistor is used to speed up the rise time of the WAIT# (TA) signal when

terminating the bus cycle.

BS# (bus start) is not used in this implementation and should be tied low (connected GND).

The following diagram shows a typical implementation of the MCF5307 to S1D13504

interface.

Figure 4-1: Typical Implementation of MCF5307 to S1D13504 Interface

Note

For pin mapping see Table 3-1:, “Generic MPU Host Bus Interface Pin Mapping” .

MCF5307

S1D13504

A[20:0]

D[31:16]

CS5

TA

WE1

WE0

OE

BCLK0

AB[20:0]

DB[15:0]

CS#

WAIT#

WE1#

WE0#

RD1#

RD0#

BUSCLK

RESET#

Vcc

470

A21

M/R#

CS4

74AC08 (or equiv.)

Note:

When connecting the S1D13504 RESET# pin, the system designer should be aware of all

conditions that may reset the S1D13504 (e.g. CPU reset can be asserted during wake-up

from power-down modes, or during debug states).

System RESET