Epson Research and Development

Page 79

Vancouver Design Center

Hardware Functional Specification

S1D13504

Issue Date: 01/11/06

X19A-A-002-19

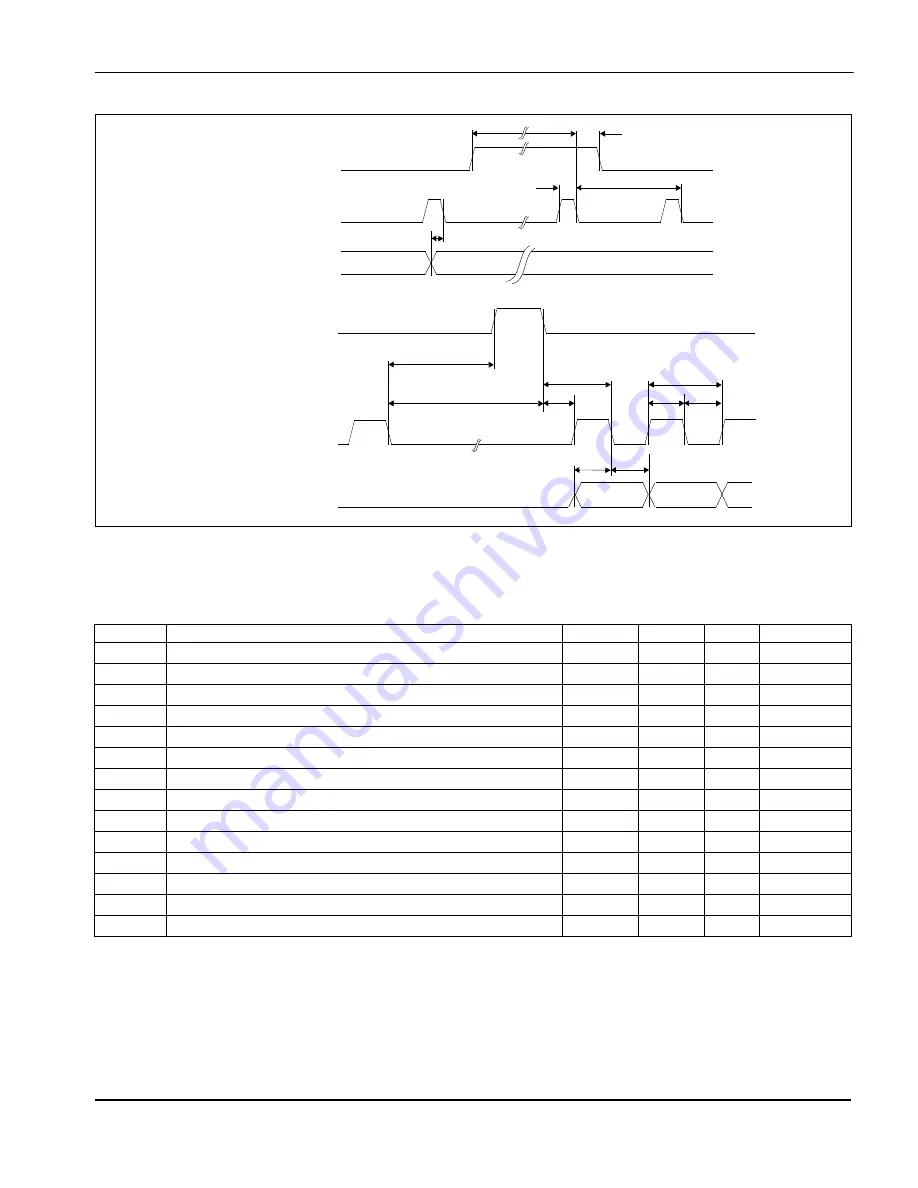

Figure 7-34: Dual Color 8-Bit Panel A.C. Timing

1.

Ts

= pixel clock period = memory clock, [memory clock]/2, [memory clock]/3, [memory clock]/4 (see REG[19h] bits [1:0])

2.

t1

min

= t3

min

- 9Ts

3.

t3

min

= [((REG[04h] bits [6:0])+1)*8 + ((REG[05h] bits [4:0]) + 1)*8] + 33 Ts

4.

t5

min

= [((REG[04h] bits [6:0])+1)*8 - 1] Ts

5.

t6

min

= [((REG[05h] bits [4:0]) + 1)*8 - 18] Ts

6.

t7

min

= [((REG[05h] bits [4:0]) + 1)*8 - 9] Ts

Table 7-26: Dual Color 8-Bit Panel A.C. Timing

Symbol

Parameter

Min

Typ

Max

Units

t1

FPFRAME setup to FPLINE falling edge

note 2

t2

FPFRAME hold from FPLINE falling edge

9

Ts (note 1)

t3

FPLINE period

note 3

t4

FPLINE pulse width

9

Ts

t5

MOD transition to FPLINE falling edge

33

note 4

Ts

t6

FPSHIFT falling edge to FPLINE rising edge

note 5

t7

FPSHIFT falling edge to FPLINE falling edge

note 6

t8

FPLINE falling edge to FPSHIFT falling edge

t14 + 1

Ts

t9

FPSHIFT period

1

Ts

t10

FPSHIFT pulse width low

0.45

Ts

t11

FPSHIFT pulse width high

0.45

Ts

t12

UD[3:0], LD[3:0] setup to FPSHIFT falling edge

0.45

Ts

t13

UD[3:0], LD[3:0] hold to FPSHIFT falling edge

0.45

Ts

t14

FPLINE falling edge to FPSHIFT rising edge

11

Ts

t12

t13

t14

t8

t9

t10

t11

1

2

Data Timing

FPFRAME

t1

t2

t3

t5

t4

FPLINE

MOD

Sync Timing

FPLINE

FPSHIFT

t7

t6

UD[3:0]

LD[3:0]